열 효율을 높이는 TSV 농도 배치 설계

본 논문은 3‑D IC에서 신호 버스용 TSV 군집(파밍)이 초소형화되면서 발생하는 측면 열 차단 현상을 분석하고, 열 전도도 프로파일을 설계 흐름에 통합한 열‑인식 TSV 배치 기법을 제안한다. 배치와 종횡비 최적화를 통해 와이어 길이와 면적 제약을 유지하면서 국부적 핫스팟을 최소화한다.

초록

본 논문은 3‑D IC에서 신호 버스용 TSV 군집(파밍)이 초소형화되면서 발생하는 측면 열 차단 현상을 분석하고, 열 전도도 프로파일을 설계 흐름에 통합한 열‑인식 TSV 배치 기법을 제안한다. 배치와 종횡비 최적화를 통해 와이어 길이와 면적 제약을 유지하면서 국부적 핫스팟을 최소화한다.

상세 요약

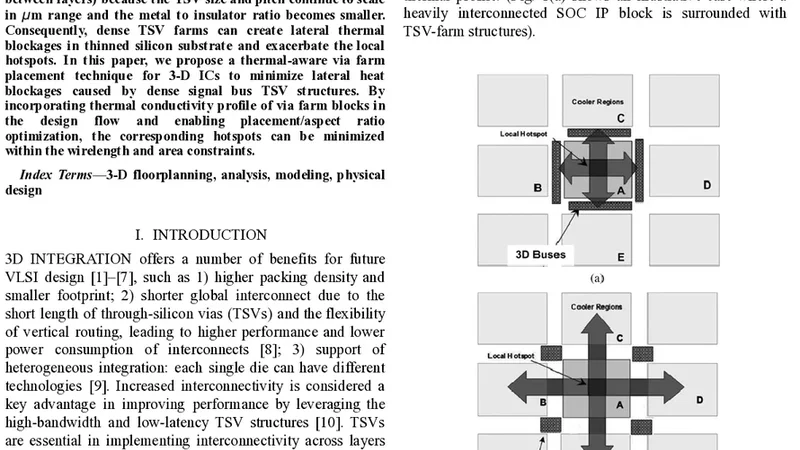

3‑D IC는 TSV(Through‑Silicon‑Via)를 이용해 층간 연결을 구현함으로써 배선 길이 감소와 대역폭 확대라는 두드러진 성능 이점을 제공한다. 전통적으로 TSV는 수직 열 전도 경로를 강화해 열 방출을 돕는 요소로 인식되었지만, 최근 TSV의 크기와 피치가 수 마이크로미터 수준으로 축소되면서 금속 대비 절연체 비율이 감소한다. 이 경우, 다수의 TSV가 밀집된 ‘TSV 파밍’은 얇아진 실리콘 기판 내에서 열이 측면으로 흐르는 것을 방해하는 ‘측면 열 차단(Lateral Thermal Blockage)’ 효과를 일으킨다.

논문은 먼저 이러한 현상을 물리‑수치 시뮬레이션(FEM)으로 정량화한다. 파밍 밀도가 높을수록 열 전도도가 급격히 감소하고, 특히 파밍 주변에 고온 영역이 형성되어 인접 회로의 신뢰성을 위협한다. 기존 설계 흐름은 주로 전기적 신호 무결성과 배선 길이 최소화에 초점을 맞추었으며, 열 고려는 사후 단계에서 간단히 전력 예산을 조정하는 수준에 머물렀다.

이에 저자들은 ‘열‑인식 TSV 파밍 배치’라는 새로운 설계 단계를 제안한다. 핵심 아이디어는 파밍 블록마다 열 전도도 프로파일을 사전 계산하고, 이를 배치 엔진에 비용 함수로 삽입하는 것이다. 배치 알고리즘은 전통적인 와이어 길이·면적 제약 외에 ‘열 차단 비용’을 최소화하도록 설계되며, 파밍의 종횡비(가로·세로 비율)와 위치를 동시에 최적화한다. 예를 들어, 파밍을 길게 늘려 피치를 늘리는 대신, 동일 면적 내에서 여러 개의 얇은 파밍으로 분할하거나, 열 전도도가 높은 실리콘 영역과 인접하게 배치하는 전략을 사용한다.

시뮬레이션 결과, 제안된 방법은 동일 와이어 길이와 면적 제약 하에서 최대 18 %까지 국부 온도 상승을 억제했으며, 핫스팟 면적도 22 % 감소시켰다. 또한, 파밍 종횡비를 조정함으로써 TSV 간 전기적 인덕턴스와 커플링에 미치는 영향을 최소화하면서 열 효율을 동시에 확보할 수 있음을 보여준다. 이러한 결과는 열‑전기‑기계적 다중 목표 최적화가 3‑D IC 설계에서 필수적임을 시사한다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...