마이크로커널 검증에서 배운 교훈 사양이 새로운 병목

초록

본 논문은 Verisoft XT 프로젝트에서 수행한 마이크로커널(L4) 검증 경험을 바탕으로, 대규모 소프트웨어 시스템의 형식 검증이 기술적인 한계보다 사양 작성 단계에서의 어려움 때문에 보편화되지 못하고 있음을 지적한다. 사양의 정확성, 완전성, 유지보수성을 확보하는 것이 현재 가장 큰 병목이며, 이를 해결하기 위한 방법론·툴·프로세스 개선 방안을 제시한다.

상세 분석

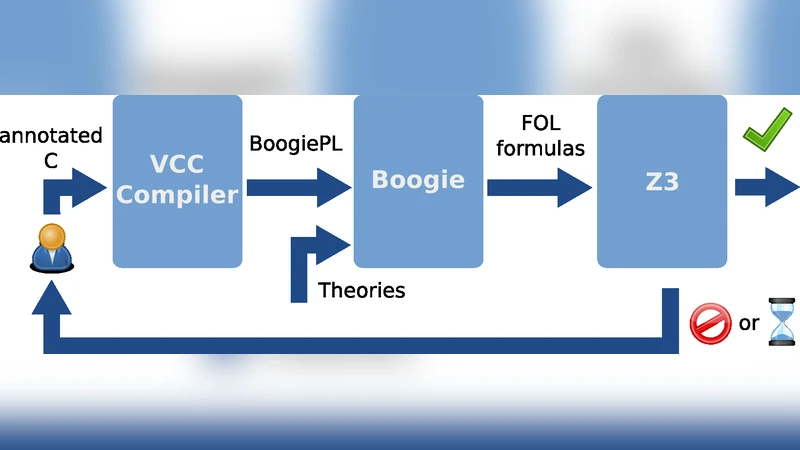

Verisoft XT 프로젝트는 L4 마이크로커널 전체를 Isabelle/HOL 기반으로 형식 검증한 선구적인 사례다. 검증 자체는 최신 자동화 도구와 증명 보조기술 덕분에 이론적으로는 가능했지만, 실제 프로젝트 진행 과정에서 가장 큰 장애물은 “사양”이었다. 첫째, 시스템 수준 사양을 작성할 때 요구사항을 충분히 추상화하면서도 구현과 일치하도록 표현하는 것이 매우 어려웠다. 추상화 레벨이 낮으면 증명 부담이 급증하고, 레벨이 높으면 사양이 실제 동작을 충분히 기술하지 못한다. 둘째, 사양의 변화 관리가 미비했다. 커널 코드가 수정될 때 사양을 동기화하는 절차가 체계화되지 않아, 오래된 사양이 남아 증명 오류의 원인이 되었다. 셋째, 사양과 구현 사이의 인터페이스 정의가 모호했다. 특히 인터럽트 처리와 스케줄링 같은 비동기 메커니즘은 형식화가 복잡해 사양이 과도하게 상세해지는 경향이 있었으며, 이는 증명 자동화 도구의 성능을 저하시켰다. 넷째, 팀원들의 사양 작성 역량 차이가 프로젝트 전체 생산성을 좌우했다. 형식 논리와 도메인 지식을 동시에 요구하는 사양 작업은 전문가가 아닌 개발자에게 큰 진입 장벽이 되었다. 마지막으로, 기존 소프트웨어 개발 프로세스와 형식 검증을 통합하는 방법론이 부재했다. 사양을 독립적인 문서로 취급하면 코드 리뷰, 테스트, CI와 연계하기 어렵고, 결과적으로 검증 결과가 실무에 반영되지 못한다. 이러한 문제들을 해결하기 위해 논문은 사양 중심의 개발 모델, 사양 자동 추출·동기화 도구, 단계적 추상화 전략, 그리고 사양 품질을 지속적으로 평가하는 메트릭스를 제안한다. 이러한 접근은 사양 작성 비용을 낮추고, 검증 결과의 신뢰성을 높이며, 형식 검증을 기존 개발 흐름에 자연스럽게 녹여낼 수 있게 한다.

댓글 및 학술 토론

Loading comments...

의견 남기기