초고다이내믹 범위 170dB 삼진 디지털‑아날로그 변환기

초록

본 논문은 32‑비트 해상도와 64 kHz 샘플링을 갖는 삼진(4R‑3R) 래더 구조 DAC를 설계·시제품화하여, 100 nV‑50 W(32 Ω 부하) 출력 범위와 약 170 dB의 동적 범위를 구현한 결과를 보고한다. 고전압·저전압 모듈을 병렬로 배치하고 MOSFET 하프‑브리지 스위치를 이용해 저노이즈·고효율을 달성했으며, 측정된 spurious‑free dynamic range는 60‑70 dB, 잡음 바닥은 열잡음에 의해 제한됨을 확인하였다.

상세 분석

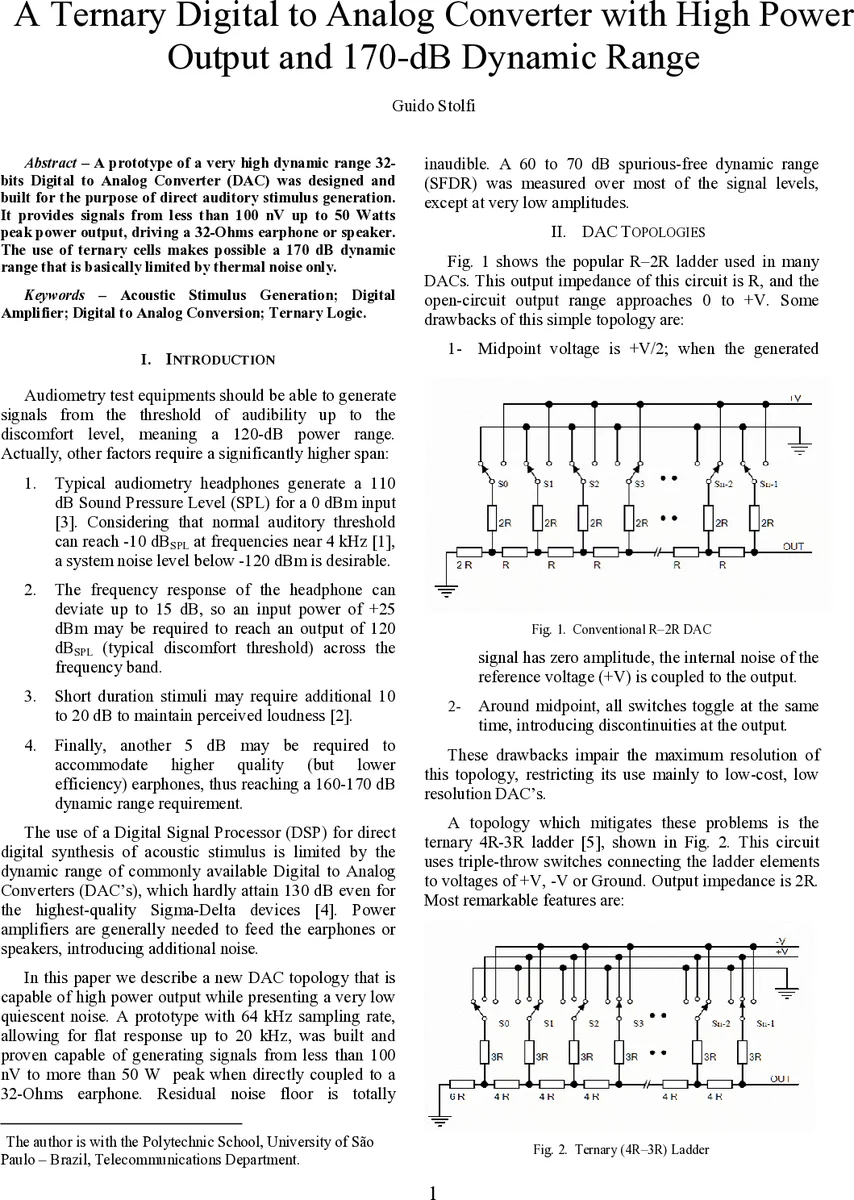

이 연구는 기존의 R‑2R DAC가 갖는 중간 전압(V/2)에서의 레퍼런스 잡음 결합 및 스위치 동시 전환에 따른 비연속성 문제를 근본적으로 해결하기 위해 삼진(4R‑3R) 래더 토폴로지를 채택한 점이 가장 큰 혁신이다. 삼진 래더는 각 단계가 +V, –V, GND 중 하나에 연결될 수 있는 3‑throw 스위치를 사용함으로써 출력 임피던스를 2R으로 고정하고, 전압 레벨이 0에 가까울 때도 레퍼런스 전압의 직접적인 잡음 유입을 최소화한다.

구현 측면에서는 20단계의 삼진 스테이지를 6개의 고전압 파워‑오브‑3 가중 스테이지, 6개의 고전압 래더, 8개의 저전압 래더로 구분하였다. 고전압 스테이지는 90 V 전원으로 구동되는 MOSFET 하프‑브리지 드라이버를 사용해 최대 50 W 피크 전력을 제공하며, 저전압 스테이지는 12 V 전원과 15 kΩ~20 kΩ 저항으로 구성해 미세 전압(수십 나노볼트) 구간에서의 전자기 결합을 억제한다. 이러한 이중 전압 구조는 고전압 단계에서 발생할 수 있는 스위치 간 누설 전류와 기생 정전용량을 저전압 단계에서 보완함으로써 전체 시스템의 잡음 플로어를 열잡음(kTB ≈ –131 dBm) 수준으로 낮춘다.

양자화 잡음 관점에서 32‑비트(20‑단계 삼진 디지털) 해상도는 이론적으로 190.8 dB의 동적 범위를 제공한다. 실제 구현에서는 저항의 5 % 허용오차와 스위치 비선형성으로 인해 SFDR이 60‑70 dB 수준에 머물렀지만, 이는 일반적인 헤드폰의 고조파 왜곡(≈30 dB)보다 충분히 우수한 수치이다. 또한 1 초 길이의 800 Hz 버스트 테스트에서 최대 전력 공급 전류가 –10 dB 출력 레벨에서 피크에 도달함을 확인했으며, 효율은 약 30 %에 달한다.

시스템 제어는 DSP가 32‑비트 고정소수점 수를 생성하고, 순차 알고리즘을 통해 20‑비트 삼진 디지털로 변환한다. 직렬‑병렬 변환기와 인터페이스 모듈은 16 비트를 고전압 모듈에, 8 비트를 저전압 모듈에 할당해 데이터 전송 지연을 최소화한다. 전체 설계는 저전력 저항과 알루미늄 차폐판을 활용해 열 관리와 전자기 간섭을 동시에 해결했으며, 연속적인 최대 전력 출력이 아닌 짧은 버스트(클릭) 용도로 설계된 점도 실용적인 선택이라 할 수 있다.

결과적으로, 이 논문은 삼진 래더와 다중 전압 스테이지를 결합한 새로운 DAC 아키텍처가 고전력 출력과 초고다이내믹 레인지(≈170 dB)를 동시에 달성할 수 있음을 실증하였다. 이는 청각계측, 고정밀 오디오 테스트, 그리고 넓은 동적 범위가 요구되는 과학·공학 분야에 중요한 기술적 기반을 제공한다.

댓글 및 학술 토론

Loading comments...

의견 남기기