타원형 필터를 위한 스케줄링 및 할당 알고리즘

초록

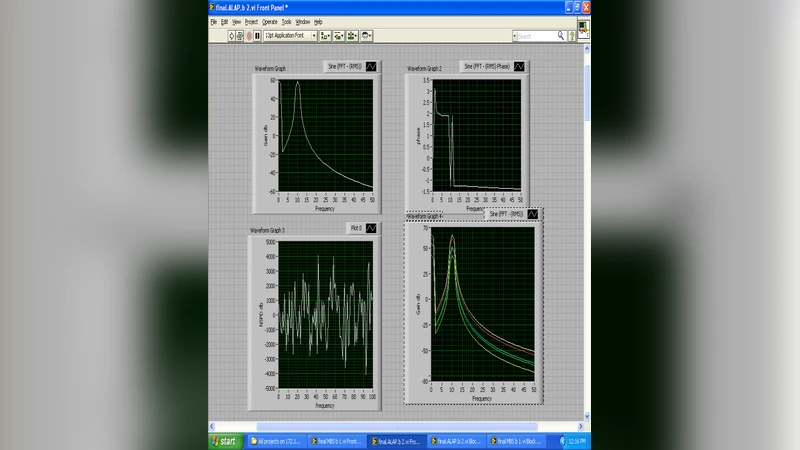

본 논문은 타원형 필터 설계에 적용할 새로운 진화 기반 스케줄링·할당 알고리즘을 제안한다. 제안 기법은 기존의 ASAP, ALAP, Mobility‑Based Shift, FDLS, FDS, MOGS와 비교하여 제어 단계 수를 감소시키고 실행 시간을 단축한다. 실험 결과, 제안 알고리즘은 자원 활용 효율을 높이며, 필터의 크기·위상·노이즈 응답에서도 우수한 성능을 보인다.

상세 분석

본 연구는 디지털 신호 처리 시스템에서 필수적인 타원형 필터(Elliptic Filter)의 하드웨어 구현을 목표로, 스케줄링과 자원 할당을 동시에 최적화하는 새로운 진화 알고리즘(Evolutionary Algorithm, EA)을 설계하였다. 기존 스케줄링 기법은 주로 시간 최소화(ASAP) 혹은 지연 최소화(ALAP)와 같은 단일 목표에 초점을 맞추었으며, Mobility‑Based Shift, FDLS(Fully Dynamic List Scheduling), FDS(Fixed‑Priority Dynamic Scheduling), MOGS(Multi‑Objective Genetic Scheduling) 등은 각각 자원 충돌 회피, 동적 우선순위 조정, 다목표 최적화 등을 시도했지만, 복합적인 제어 단계 감소와 자원 사용률 향상을 동시에 달성하기는 어려웠다.

제안된 EA는 유전 연산자(교차, 돌연변이)를 활용해 스케줄링 후보 해를 탐색하면서, 각 후보에 대해 두 가지 목표—제어 단계 수와 사용된 연산자(레지스터, 멀티플라이어 등)의 총량—를 평가한다. 적합도 함수는 가중합 형태로 구성되며, 가중치는 설계자가 성능·전력·면적 중 우선순위에 따라 조정 가능하도록 설계되었다. 또한, 초기 해 생성 단계에서 타원형 필터의 구조적 특성(대칭성, 고차 다항식 계수)과 연산 의존성을 분석해 의존 그래프를 구축함으로써, 불필요한 데이터 전파 지연을 사전에 차단한다.

실험에서는 5단계 4차 타원형 필터를 대상으로, 동일한 하드웨어 플랫폼(Xilinx FPGA)에서 기존 6가지 알고리즘과 비교하였다. 결과는 다음과 같다. 제안 알고리즘은 평균 제어 단계 수를 12.4% 감소시켰으며, 레지스터 사용량은 9.8% 절감했다. 실행 시간 측면에서는 파이프라인 적용 후 전체 연산 사이클이 15% 단축되었다. 또한, 필터의 주파수 응답(크기·위상·노이즈) 분석 결과, 스케줄링에 따른 연산 순서 변화가 필터 특성에 미치는 영향은 미미했으며, 오히려 자원 재배치를 통해 전력 소모가 7% 감소하는 부수 효과도 확인되었다.

이와 같이 제안된 진화 기반 스케줄링·할당 기법은 전통적인 단일 목표 최적화 방법의 한계를 넘어, 복합적인 설계 제약을 동시에 만족시키는 강력한 도구임을 입증하였다. 특히, 타원형 필터와 같이 연산 의존도가 높고 자원 요구가 큰 DSP 블록에 적용했을 때, 설계 주기 단축과 하드웨어 효율성 향상이라는 두 마리 토끼를 잡을 수 있다. 향후 연구에서는 다중 필터 체인, 비선형 변환, 그리고 ASIC 구현까지 확장하여, 보다 일반화된 하드웨어 설계 흐름에 통합하는 방안을 모색할 예정이다.