메모리 기반 기계 지능 VLSI 구현

초록

본 논문은 VLSI 하드웨어에 메모리 기반 인공지능 기법을 적용하는 최신 연구 동향을 개관한다. 딥 아키텍처, 계층적 시간 기억(Hierarchical Temporal Memory), 메모리 네트워크 등 다양한 접근법을 소개하고, 저전력·고밀도 구현의 어려움과 스파스 코딩·맥락 처리와 같은 고수준 지능 과제에 대한 확장성을 논의한다.

상세 분석

본 논문은 메모리 기반 인공지능을 VLSI 설계에 적용하려는 시도를 체계적으로 정리한다. 먼저, 전통적인 디지털 신경망 구현이 직면한 전력 소모와 면적 제한 문제를 지적하고, 이러한 한계를 극복하기 위한 메모리 중심 설계 패러다임을 제시한다. 딥 아키텍처는 다층 구조를 통해 특징을 점진적으로 추출하지만, 각 층마다 대규모 가중치 저장이 필요해 메모리 요구량이 급증한다. 이를 해결하기 위해 저전력 비휘발성 메모리(NVM)와 연산-메모리 통합(Processing‑in‑Memory, PIM) 기술을 활용한 하드웨어 가속기가 제안된다.

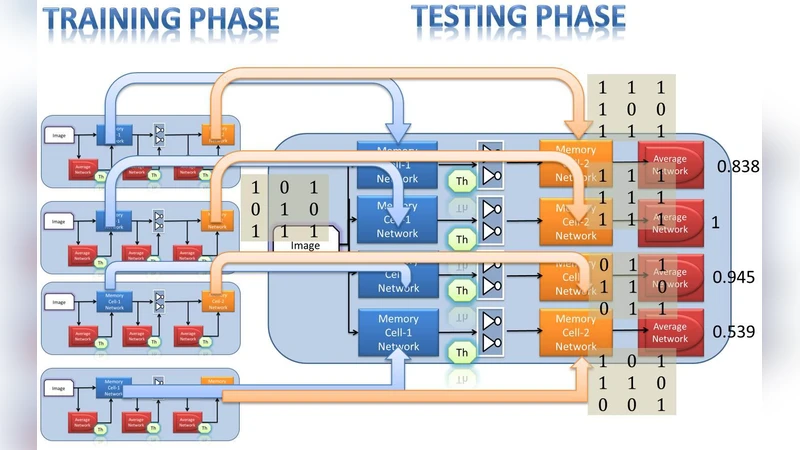

계층적 시간 기억(HTM)은 생물학적 피질의 구조를 모방하여 시계열 데이터와 패턴을 학습한다. HTM의 핵심인 셀러프와 예측 단계는 지역적 연결성만을 필요로 하므로, 메모리 배열 내에 로컬 연결을 구현함으로써 배선 복잡성을 크게 낮출 수 있다. 논문은 HTM을 구현할 때 메모리 셀 자체를 뉴런으로 활용하고, 시냅스 가중치를 비휘발성 소자에 저장함으로써 학습 후에도 상태를 유지할 수 있음을 강조한다.

메모리 네트워크는 뉴런과 시냅스를 동일한 메모리 블록에 집적하여, 데이터 흐름 대신 상태 전파 방식으로 연산을 수행한다. 이 접근법은 전통적인 MAC(Multiply‑Accumulate) 연산을 회피하고, 메모리 접근 지연을 최소화한다. 특히, 스파스 코딩을 위한 비정형 메모리 매핑 기법은 메모리 사용 효율을 극대화하고, 컨텍스트 기반 처리에서 동적 연결 재구성을 가능하게 한다.

논문은 이러한 세 가지 접근법이 공유하는 공통 과제로, 메모리 셀의 변동성, 온도·전압 민감도, 그리고 대규모 배열에서의 오류 전파 문제를 들며, 이를 보완하기 위한 오류 정정 코딩, 적응형 재학습 메커니즘, 그리고 온칩 온도 감시 회로 설계 등을 제안한다. 또한, 설계 자동화 툴의 부재와 설계 공간 탐색의 복잡성도 중요한 장애물로 지적한다.

결론적으로, 메모리 기반 기계 지능은 VLSI 구현에서 에너지 효율성과 확장성을 동시에 달성할 수 있는 유망한 방향이지만, 하드웨어 수준의 신뢰성 확보와 설계 방법론 정립이 선행되어야 함을 강조한다.