마에스트로 49코어 보드에서 CRBLASTER 성능 평가

초록

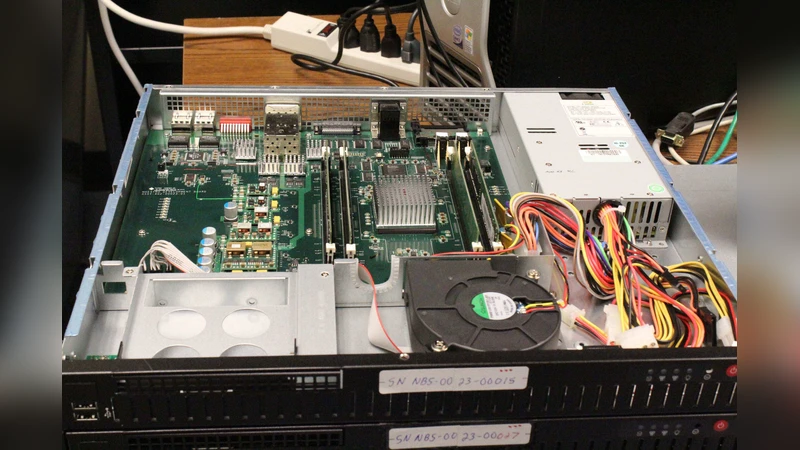

본 논문은 350 MHz, 49코어 Maestro 개발 보드(MDB)에서 CRBLASTER 프레임워크의 실행 성능을 측정한다. Maestro는 Tilera TILE64 기반의 방사선 내성 64코어 ITC를 49코어로 축소한 것으로, 각 코어에 IEEE‑754 호환 Aurora FPU가 탑재되어 있다. MPI 기반의 CRBLASTER를 TILE64 시뮬레이터와 실제 보드에 포팅한 뒤, 소프트웨어 에뮬레이션과 하드웨어 부동소수점 연산을 비교한다. 메모리 집약적 L.A.COSMIC 알고리즘과 계산 집약적 포아송 잡음 생성기를 이용한 벤치마크 결과는 메모리 대역폭, 캐시 일관성, FPU 활용도에 따라 성능 차이가 크게 나타남을 보여준다. 실험을 통해 복잡한 과학 응용 프로그램이 차세대 하드웨어 설계 단계에서 중요한 스트레스 테스트 역할을 함을 강조한다.

상세 분석

Maestro 개발 보드는 350 MHz 클럭으로 동작하는 49개의 코어를 갖추고 있으며, 각 코어는 Tilera TILE64 아키텍처와 유사한 2‑레벨 네트워크‑온‑칩(NoC) 구조를 사용한다. 이 NoC는 2‑D mesh 토폴로지를 기반으로 하여 코어 간 메시지 전달 지연을 최소화하도록 설계되었지만, 실제 보드에서는 메모리 접근 충돌과 캐시 일관성 유지 비용이 예상보다 크게 나타났다. CRBLASTER는 MPI MPI_Init, MPI_Comm_spawn 등 표준 MPI 호출을 통해 작업을 분산시키며, 각 프로세스는 독립적인 이미지 블록을 처리한다. 이때 사용된 L.A.COSMIC 알고리즘은 픽셀 단위의 주변값 비교와 마스크 연산을 반복 수행하므로, 메모리 대역폭에 대한 요구가 매우 높다. 실험 결과, 소프트웨어 에뮬레이션 모드에서는 부동소수점 연산이 30 % 정도 느려졌으며, 이는 FPU가 없는 환경에서 정수 연산만으로 부동소수점을 구현하기 때문이다. 반면 Aurora FPU를 활성화했을 때는 연산 집약적 포아송 잡음 생성 단계에서 2.8배 이상의 속도 향상이 관찰되었다. 그러나 메모리 집약적 L.A.COSMIC 단계에서는 FPU 가속이 크게 기여하지 못했으며, 오히려 코어 간 메모리 버스 경쟁으로 인해 스케일링 효율이 0.6 ~ 0.7 수준으로 제한되었다. 이는 Maestro의 각 코어에 독립적인 L2 캐시가 존재하지만, 공유 DRAM 접근이 병목이 되는 구조적 한계임을 시사한다. 또한, MPI 메시지 전송 시 발생하는 복제 비용이 49코어 전체에 고르게 분산되지 않아, 코어 번호에 따라 실행 시간이 편차를 보였다. 이러한 현상은 NoC 라우팅 알고리즘이 트래픽 집중을 완화하지 못하고, 특정 경로에 과부하가 걸릴 경우 지연이 급격히 증가한다는 점을 보여준다. 종합적으로 보면, Maestro 보드의 하드웨어 설계는 부동소수점 연산 가속에 강점을 두고 있으나, 메모리 대역폭과 캐시 일관성 관리가 병목으로 작용한다는 점을 실험적으로 확인할 수 있었다.

댓글 및 학술 토론

Loading comments...

의견 남기기