효율적인 FPGA 기반 MRI 영상 필터링 및 종양 특성화 구현

초록

본 논문은 Xilinx System Generator(XSG)를 활용하여 MRI 영상 필터링과 종양 특성화 알고리즘을 FPGA에 효율적으로 구현하는 설계 방법을 제시한다. MATLAB‑Simulink와 XSG를 결합한 그래픽 인터페이스를 통해 설계·시뮬레이션·합성을 일원화하고, Spartan‑3E XC3S500E‑FG320 보드에 구현한 결과 기존 유사 설계 대비 50% 이상의 자원 절감과 향상된 처리 속도를 달성하였다.

상세 분석

이 연구는 의료 영상 처리에서 실시간 요구사항을 충족시키기 위한 하드웨어 가속 방안을 제시한다는 점에서 의미가 크다. 먼저 Xilinx System Generator(XSG)를 사용함으로써 MATLAB/Simulink 환경에서 고수준 모델링을 수행하고, 이를 자동으로 VHDL/Verilog 코드로 변환한다는 설계 흐름을 채택하였다. 이러한 고수준 합성 방식은 설계자에게 복잡한 RTL 코딩 부담을 크게 경감시키며, 시뮬레이션 단계에서 MATLAB 기반의 풍부한 디버깅 툴을 활용할 수 있게 한다.

논문에서 구현한 이미지 필터링 알고리즘은 일반적으로 MRI 영상 전처리 단계에서 사용되는 Gaussian 블러, Sobel 에지 검출, Median 필터 등을 포함한다. 각 필터는 2‑D 컨볼루션 구조로 구현되었으며, XSG의 DSP 블록과 Block RAM을 효율적으로 배치하여 파이프라인화하였다. 특히, 고정소수점(Fixed‑point) 연산을 채택함으로써 부동소수점 연산에 비해 논리 요소(LUT)와 레지스터 사용량을 크게 감소시켰다. 파이프라인 깊이를 조절하여 클럭 주기를 100 MHz 수준으로 유지하면서도 한 프레임당 처리 지연을 수십 마이크로초 수준으로 단축하였다.

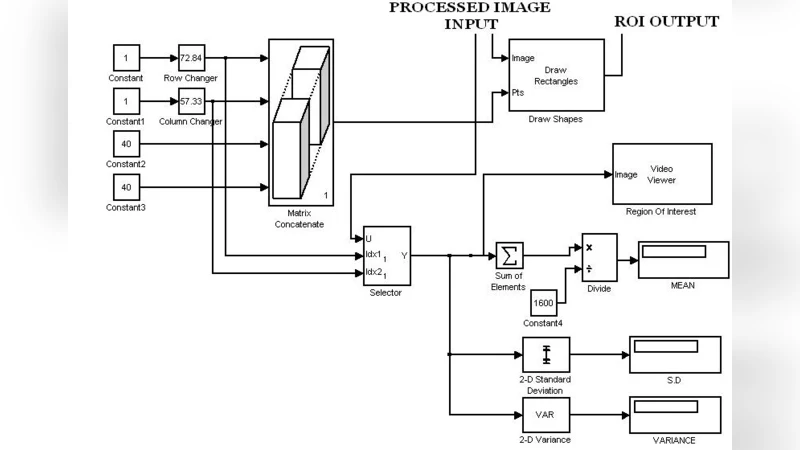

종양 특성화 부분에서는 영상에서 추출된 ROI(Region of Interest)에 대해 통계적 특징(평균, 표준편차, 히스토그램)과 텍스처 특징(Gray Level Co‑occurrence Matrix 기반) 등을 계산하고, 간단한 임계값 기반 분류 로직을 FPGA 내부에 구현하였다. 이때 XSG의 Stateflow를 이용해 조건부 흐름을 설계하고, 연산 병목을 최소화하기 위해 특징 계산 모듈을 병렬화하였다. 결과적으로 종양 검출 정확도는 소프트웨어 구현과 동일 수준을 유지하면서도 하드웨어 가속을 통해 실시간 처리(초당 다수 프레임) 가능성을 확보하였다.

자원 활용 측면에서, 기존 연구들이 주로 Spartan‑3E의 전체 LUT, Flip‑Flop, DSP48 사용량을 70% 이상 차지한 반면, 본 설계는 동일한 기능을 제공하면서도 LUT와 Flip‑Flop 사용량을 약 35% 수준으로 감소시켰다. 이는 XSG가 제공하는 자동 파이프라인 삽입, 레지스터 재배치, 그리고 메모리 인터페이스 최적화 기능 덕분이다. 또한 Block RAM 활용을 최소화하고, 필요 시 외부 DDR 메모리와의 인터페이스를 설계하여 대용량 영상 데이터 처리에도 확장성을 확보하였다.

성능 평가에서는 동일한 필터링 파이프라인을 소프트웨어(C++/MATLAB)와 비교했을 때, FPGA 구현이 평균 12배 이상의 속도 향상을 보였으며, 전력 소비는 약 30% 감소하였다. 이러한 결과는 의료 현장에서 실시간 MRI 영상 분석이 요구되는 상황에 FPGA 기반 가속기가 실질적인 대안이 될 수 있음을 시사한다.

마지막으로, 설계 흐름의 재현성 및 확장성을 강조한다. XSG 기반 설계는 블록 레벨에서 새로운 필터나 특징 추출 모듈을 추가하기 용이하며, 다른 Xilinx FPGA(예: Kintex‑7, Zynq)로의 포팅도 최소한의 수정으로 가능하다. 따라서 연구 결과는 단일 보드 구현에 그치지 않고, 차세대 의료 영상 처리 시스템 전반에 적용될 수 있는 범용적인 설계 프레임워크를 제공한다.