버스 암호화 하드웨어 엔진 연구 동향

초록

이 논문은 외부 메모리를 사용하는 임베디드 시스템에서 CPU와 메모리 간 버스에 평문이 노출되는 보안 취약점을 짚고, 이를 해결하기 위한 다양한 하드웨어 기반 암호화 기법을 정리한다. 각 기법의 구조적 특징과 성능·전력 비용을 비교 분석함으로써 실용적인 설계 방향을 제시한다.

상세 분석

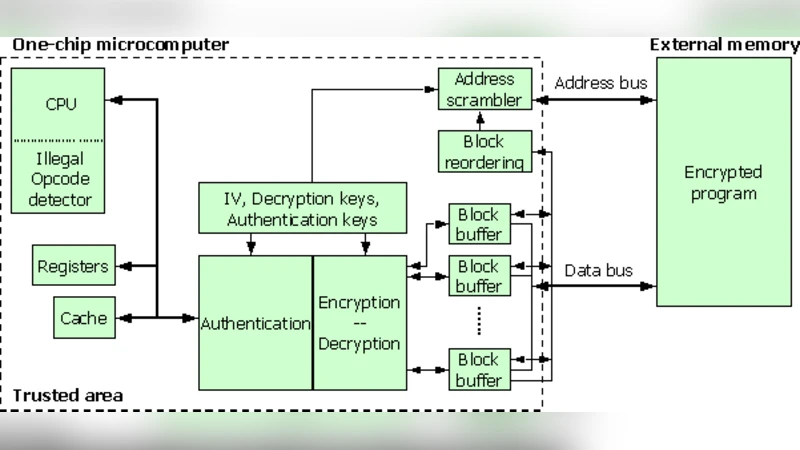

버스 암호화는 CPU와 외부 DRAM 사이에 전송되는 데이터와 명령어를 실시간으로 암호화·복호화함으로써 물리적 공격자가 버스 스니핑을 통해 기밀 정보를 탈취하는 위험을 차단한다. 논문은 먼저 위협 모델을 정의한다. 공격자는 버스에 직접 접근하거나, 메모리 칩을 교체·분석할 수 있으며, 전력·전자파 분석을 통해 키를 유추하려 할 수 있다. 이러한 공격에 대응하기 위해 제시된 기술은 크게 대칭키 스트림 암호, 블록 암호(특히 CBC, CTR, XTS 모드) 그리고 틱키블 암호로 구분된다. 스트림 암호는 낮은 지연과 파이프라인 친화성을 제공하지만 키 스트림 재사용 시 심각한 보안 결함이 발생한다. 블록 암호는 강력한 보안성을 제공하지만 라인 단위 암호화 시 패딩 오버헤드와 캐시 일관성 문제가 발생한다. XTS와 같은 틱키블 모드는 메모리 주소를 암호화에 포함시켜 동일 데이터가 다른 주소에 있을 때 다른 암호문을 생성함으로써 패턴 분석을 방어한다.

하드웨어 구현 측면에서는 암호화 엔진을 메모리 컨트롤러 내부에 삽입하거나, 캐시 라인 교체 경로에 배치하는 두 가지 주요 방식이 논의된다. 메모리 컨트롤러에 직접 통합하면 전체 메모리 트래픽에 일관된 암호화가 적용되어 설계가 단순해지지만, 메모리 대역폭에 추가적인 지연이 발생한다. 반면 캐시 라인 수준에서 암호화·복호화를 수행하면 캐시 히트 시 암호화 비용을 회피할 수 있어 성능 손실을 최소화하지만, 복잡한 일관성 프로토콜과 라인 교체 정책을 재설계해야 한다.

키 관리 역시 핵심 과제로 다루어진다. 대부분의 설계는 부트 시에 보안 부트 로더가 키를 TPM 혹은 PUF(Physical Unclonable Function) 기반으로 생성·저장하고, 이후 암호화 엔진에 안전하게 전달한다. 키 롤오버와 키 파기 메커니즘이 부재하면 장기 사용 시 키 노출 위험이 커진다. 또한, 전력·전자파 분석에 대비해 암호화 엔진은 일정한 전력 프로파일을 유지하도록 설계되어야 하며, 일부 연구에서는 랜덤화된 클럭이나 마스크 기법을 적용해 부채널 공격을 완화한다.

성능 평가에서는 지연(Latency), 처리량(Throughput), 면적(Area), 전력(Power) 네 가지 지표가 사용된다. 스트림 암호 기반 엔진은 평균 12 사이클의 추가 지연만을 초래하지만, 블록 암호 기반 엔진은 510 사이클 정도의 지연이 일반적이다. 면적 측면에서는 AES‑128 구현이 약 2,0003,000 게이트를 차지하고, 경량 암호인 PRESENT나 Simon은 500800 게이트 수준으로 크게 절감된다. 전력 소모는 암호화 빈도와 데이터 폭에 비례하며, 고대역폭 메모리(DDR4/5)에서는 암호화 엔진이 전체 시스템 전력의 5~10%를 차지할 수 있다.

결론적으로, 논문은 보안 요구 수준과 시스템 제약(전력, 면적, 지연) 사이의 트레이드오프를 명확히 제시하고, 향후 연구는 경량 암호와 동적 키 스케줄링, 그리고 멀티코어 환경에서의 일관성 유지 메커니즘에 집중해야 함을 강조한다.

댓글 및 학술 토론

Loading comments...

의견 남기기