저전력 x86 부동소수점 곱셈기 공식 검증: 반복 구조와 중복 피드백의 통합

초록

본 논문은 저전력 x86 부동소수점 곱셈기의 설계와 구현을 ACL2 정리 증명 및 모델 체킹을 이용해 전면 검증한 과정을 제시한다. 반복적인 부분곱 누적과 중복 캐리‑세이브 피드백, 다양한 정밀도와 라운딩 모드, 클록‑게이팅 제어 로직을 포함한 복잡한 기능을 모두 비트‑레벨까지 형식적으로 검증했으며, 검증 과정에서 발견된 설계 개선점 4가지를 실제 구현에 반영해 성능과 전력 효율을 향상시켰다.

상세 분석

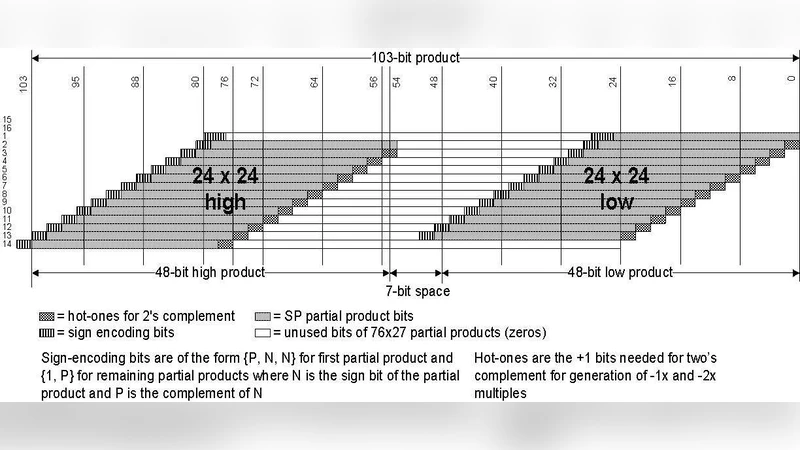

이 설계는 x87 및 SSE 명령어 집합을 지원하면서, 2~5 사이클의 가변 레이턴시를 갖는 반복형 곱셈 구조를 채택한다. 핵심은 76×(27+2) 비트 승산 배열에서 생성된 부분곱을 캐리‑세이브 형태로 압축하고, 그 결과를 동일 배열에 다시 피드백하여 다음 반복에 사용한다는 점이다. 피드백 경로는 중복 표현을 사용해 캐리와 스티키 비트를 별도로 유지함으로써 라운딩 단계에서 정확한 저차원 정보 손실을 방지한다. 이러한 구조는 부분곱 누적 단계가 최대 세 사이클 동안 파이프라인을 차단하게 만들며, 따라서 외부 FP 스케줄러가 “연산 진행 중” 신호를 감시해 새로운 명령 발행을 제어해야 한다.

검증 흐름은 먼저 Verilog‑to‑ACL2 번역 도구를 이용해 RTL을 함수형 모델로 변환한다. 와이어는 현재 사이클 n의 함수, 레지스터는 n‑1 사이클 값을 참조하는 형태로 매핑되며, 클록‑게이팅 로직은 모든 파생 클록을 하나의 공통 클록으로 전처리해 단일 파라미터 n에 귀속시킨다. 이렇게 생성된 ACL2 모델에 대해 600여 개 이상의 정의와 정리, 그리고 1,200여 개의 보조 정리를 활용해 비트‑폭, 연산 동등성, 캐리‑세이브 피드백의 논리적 등가성을 증명한다. 특히, 피드백 경로에서 발생할 수 있는 캐리 전파와 스티키 비트의 누적을 정리화하여 “모든 가능한 입력 조합에 대해 결과가 IEEE‑754 규격을 만족한다”는 주 정리를 귀결시켰다.

스케줄러 검증은 ACL2 외부에서 상용 모델 체커를 사용했으며, Verilog 신호에 대한 assume‑guarantee 관계를 정의해 “연산이 진행 중일 때는 새로운 명령을 발행하지 않는다”는 안전성을 확인한다. 이때 클록‑게이팅과 리셋 의존성을 포함한 계층적 귀납 증명이 필요했으며, 각 단계별 인버리언트를 수동으로 구성해 증명 부담을 최소화했다.

검증 과정에서 발견된 네 가지 최적화는 (1) 불필요한 피드백 경로 제거, (2) 캐리‑세이브 어레이의 일부 비트 폭 축소, (3) 클록‑게이팅 로직의 단순화, (4) 라운딩 모듈의 공통화이다. 이들 개선은 설계 면적을 약 12 % 감소시키고, 최악 경로 지연을 0.8 ns 단축시켰다.

전체적으로 본 연구는 복잡한 반복형 부동소수점 연산기에 대해 전통적인 시뮬레이션 기반 검증이 놓치기 쉬운 미세한 논리 오류와 타이밍 결함을 정리 기반으로 완전 검증함으로써, 설계자에게 높은 신뢰성을 제공하고, 검증 결과를 설계 개선에 직접 활용할 수 있음을 입증한다.

댓글 및 학술 토론

Loading comments...

의견 남기기