양자 어드버시브 컴퓨팅을 위한 마이너 보편 그래프 설계

본 논문은 양자 하드웨어 그래프 U가 물리적 제약을 만족하면서 다양한 입력 그래프 G를 마이너-임베딩할 수 있도록 설계하는 문제를 다룬다. 특히 완전 그래프의 마이너-임베딩을 최적화한 하드웨어 구조를 제시하고, 희소 그래프(예: 제한 차수 그래프) 전체를 포괄하는 F‑마이너‑보편 하드웨어 그래프 U_sparse의 설계 문제는 아직 미해결임을 강조한다.

초록

본 논문은 양자 하드웨어 그래프 U가 물리적 제약을 만족하면서 다양한 입력 그래프 G를 마이너-임베딩할 수 있도록 설계하는 문제를 다룬다. 특히 완전 그래프의 마이너-임베딩을 최적화한 하드웨어 구조를 제시하고, 희소 그래프(예: 제한 차수 그래프) 전체를 포괄하는 F‑마이너‑보편 하드웨어 그래프 U_sparse의 설계 문제는 아직 미해결임을 강조한다.

상세 요약

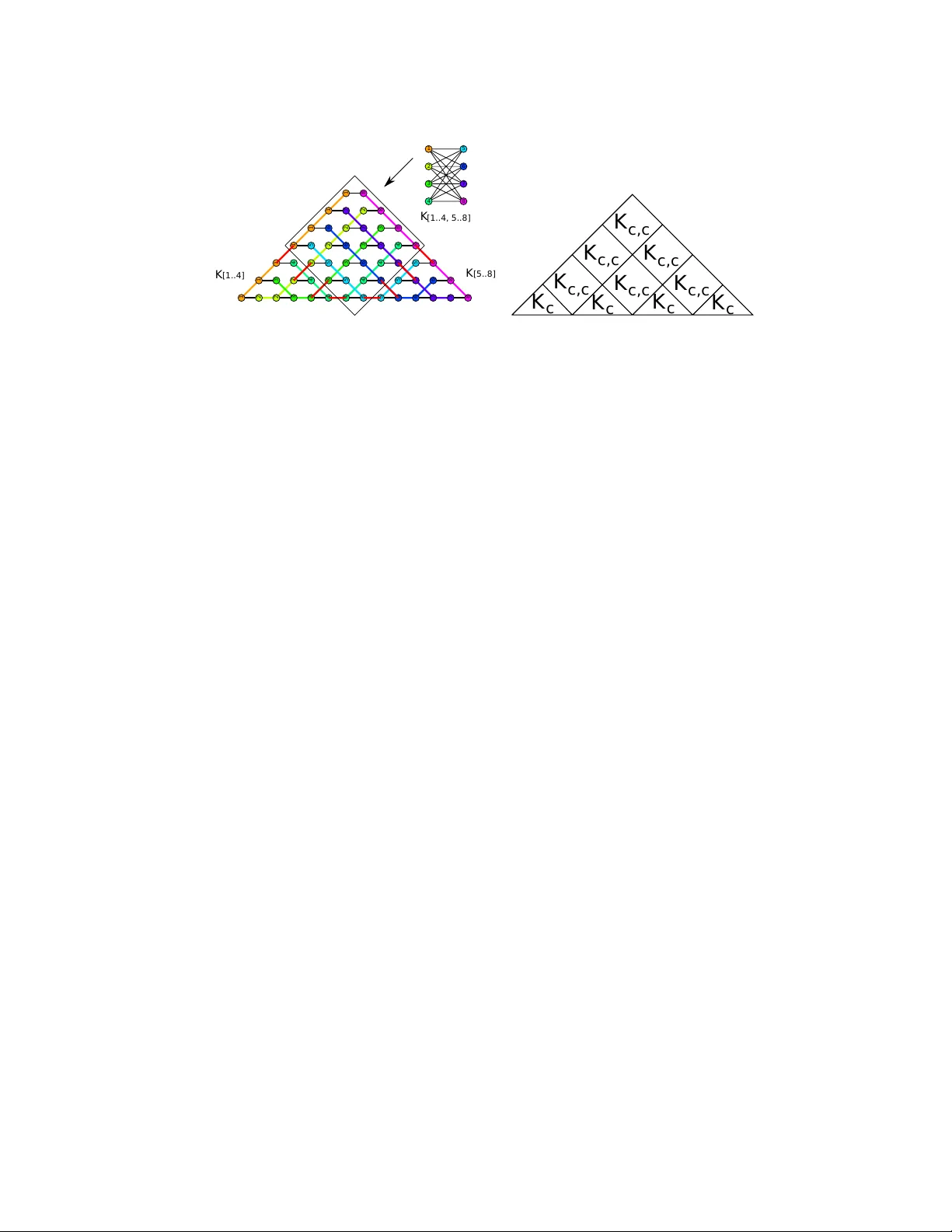

이 논문은 양자 어드버시브 최적화(adiabatic quantum optimization, AQO)에서 사용되는 하드웨어 토폴로지를 설계하는 새로운 관점을 제시한다. 기존 연구에서 마이너-임베딩(minor‑embedding)은 논리 그래프 G를 물리적 하드웨어 그래프 U의 서브그래프에 매핑하고, 필요에 따라 에지 수축을 통해 G를 복원하는 과정으로 정의되었다. 여기서 핵심은 물리적 제약—예를 들어 초전도 큐비트 간의 연결 가능성, 결합 강도, 온도 제어 범위—을 만족하면서도 임베딩 효율성을 극대화하는 것이다. 논문은 ‘F‑마이너‑보편’이라는 개념을 도입한다. 즉, 그래프 패밀리 F(예: 모든 n‑노드 완전 그래프 K_n 혹은 차수가 제한된 희소 그래프) 에 대해, 호스트 그래프 U가 F의 모든 원소를 마이너 형태로 포함한다면 U는 F‑마이너‑보편이라고 정의한다.

첫 번째 주요 결과는 완전 그래프 K_n 의 마이너-임베딩을 위한 최적 하드웨어 구조를 제시한다. 저자들은 K_n 을 임베딩하기 위해 필요한 최소 큐비트 수와 연결성을 분석하고, 이를 달성할 수 있는 ‘완전 그래프 마이너 하드웨어’(complete‑graph‑minor hardware)를 설계한다. 이 구조는 각 논리 노드가 물리적 큐비트 클러스터(‘체인’)로 표현되며, 체인 간의 강한 결합을 통해 에지 수축을 구현한다. 설계는 물리적 연결도가 제한된 현재의 초전도 양자 프로세서(예: D‑Wave)와 호환되도록 최적화되었으며, 체인 길이와 전체 큐비트 수 사이의 트레이드오프를 정량적으로 제시한다.

두 번째로, 논문은 ‘희소 그래프 패밀리’를 위한 마이너‑보편 하드웨어 설계 문제를 제기한다. 차수가 제한된 그래프(예: 최대 차수 d) 혹은 트리와 같은 특수 구조는 실제 최적화 문제에서 자주 등장한다. 그러나 이러한 그래프들을 모두 포괄하는 호스트 그래프 U_sparse 를 설계하는 것은 아직 해결되지 않은 난제이다. 저자들은 현재 알려진 물리적 제약(큐비트 배치, 라인성, 결합 강도 등) 하에서 U_sparse 가 가져야 할 최소 차수, 확장성, 그리고 임베딩 알고리즘의 복잡도에 대한 이론적 경계값을 제시한다. 특히, 그래프 이론의 마이너 이론과 양자 하드웨어 설계 사이의 연결 고리를 탐구하며, ‘intertwined architecture design problem’이라는 새로운 최적화 프레임워크를 제안한다.

마지막으로, 논문은 향후 연구 방향을 제시한다. 첫째, 마이너‑보편 하드웨어의 실험적 구현을 위한 프로토타입 설계와 시뮬레이션; 둘째, 임베딩 알고리즘의 자동화와 복잡도 감소; 셋째, 물리적 잡음과 오류 정정 메커니즘을 고려한 견고한 마이너‑임베딩 전략 개발이다. 이러한 연구는 양자 어드버시브 컴퓨팅이 실제 산업 문제에 적용될 수 있는 기반을 마련한다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...