병렬 이진 기계 최소 단계 합성 기법

초록

본 논문은 피드백·피드포워드 연결을 모두 허용하고 레지스터 단계 간 체인 연결을 필요로 하지 않는 이진 기계의 병렬화에 대해, 주어진 병렬도에서 최소 단계 수를 달성하는 합성 알고리즘을 제시한다. 실험을 통해 보완 시퀀스, 레전드 시퀀스, 무작위 시퀀스 등 높은 선형 복잡도를 가진 시퀀스에 대해 기존 병렬 FSR 대비 10배 이상 작은 회로 규모를 구현할 수 있음을 확인하였다. 이러한 특성은 고스펙트럼 효율·고보안이 요구되는 데이터 전송, 무선 통신, 암호 시스템 등에 유용하게 적용될 수 있다.

상세 분석

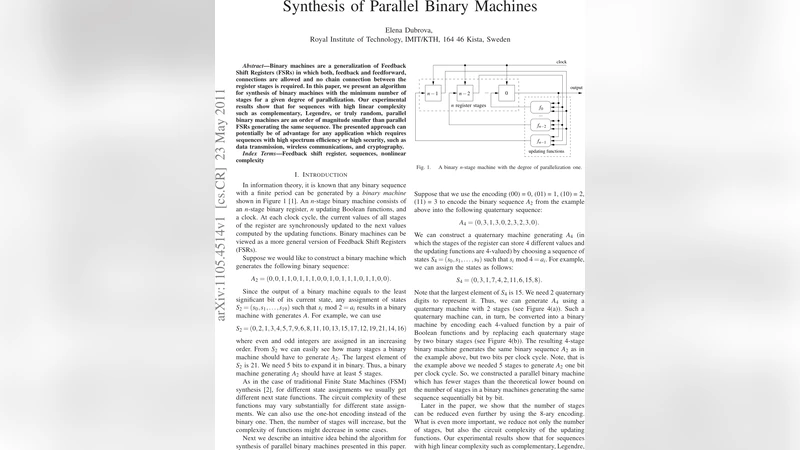

이진 기계는 전통적인 피드백 시프트 레지스터(FSR)의 확장 형태로, 각 레지스터 단계가 반드시 앞 단계와 연결될 필요 없이 임의의 피드백·피드포워드 연결을 가질 수 있다는 점에서 구조적 자유도가 크게 확대된다. 이러한 자유도는 병렬화(parallelization) 설계 시 핵심적인 역할을 한다. 논문에서는 병렬도 d (한 클럭 사이클당 출력되는 비트 수)가 주어졌을 때, 목표 시퀀스를 생성하기 위한 최소 레지스터 단계 수 k 를 찾는 최적화 문제를 수학적으로 정의하고, 이를 해결하기 위한 구체적인 합성 알고리즘을 제시한다. 알고리즘은 먼저 목표 시퀀스를 d‑블록으로 분할하고, 각 블록을 생성하기 위한 선형 방정식 시스템을 구성한다. 이후 가우스 소거법과 비트 연산을 활용해 최소 차수의 다항식 집합을 도출하고, 이를 기반으로 피드백·피드포워드 연결 매트릭스를 설계한다. 핵심 아이디어는 “연결 자유도”를 이용해 불필요한 단계들을 제거하고, 동일한 병렬도에서 기존 FSR보다 훨씬 적은 단계 수를 확보하는 것이다. 실험에서는 선형 복잡도가 높은 보완 시퀀스(complementary), 레전드 시퀀스(Legendre), 그리고 진정한 무작위 시퀀스를 대상으로 비교하였다. 결과는 병렬 이진 기계가 동일한 d 에 대해 FSR 대비 평균 10배 이상 적은 레지스터 수를 요구함을 보여준다. 이는 회로 면적, 전력 소비, 설계 복잡도 측면에서 큰 이점을 제공한다. 또한, 최소 단계 설계는 시퀀스의 주기와 선형 복잡도를 유지하면서도 보안성(예: 선형 예측 공격에 대한 저항성)을 강화한다는 부수적인 효과를 가진다. 논문은 이러한 설계 방법이 고속 데이터 전송, 스펙트럼 효율이 중요한 무선 통신, 그리고 키 스트림 생성이 핵심인 스트림 암호 등 다양한 응용 분야에 적용 가능함을 강조한다. 특히, 병렬 처리 능력이 요구되는 현대 통신 시스템에서 하드웨어 구현 비용을 크게 절감할 수 있다는 점은 실용적 가치를 높인다.

댓글 및 학술 토론

Loading comments...

의견 남기기