전류미러 회로를 이용한 얇은막 트랜지스터 배열 설계

본 논문은 4×4 TFT 매트릭스에 전류미러 증폭기를 적용하여 스위치 수를 감소시키고 변환 시간을 단축시킨 설계 및 구현 방법을 제시한다. 전류미러 회로를 통해 16개의 픽셀 신호를 하나의 노드에서 직접 합산함으로써 인접 픽셀의 광강도 합산을 가능하게 하였으며, 제작 및 테스트 결과 정상 동작을 확인하였다.

초록

본 논문은 4×4 TFT 매트릭스에 전류미러 증폭기를 적용하여 스위치 수를 감소시키고 변환 시간을 단축시킨 설계 및 구현 방법을 제시한다. 전류미러 회로를 통해 16개의 픽셀 신호를 하나의 노드에서 직접 합산함으로써 인접 픽셀의 광강도 합산을 가능하게 하였으며, 제작 및 테스트 결과 정상 동작을 확인하였다.

상세 요약

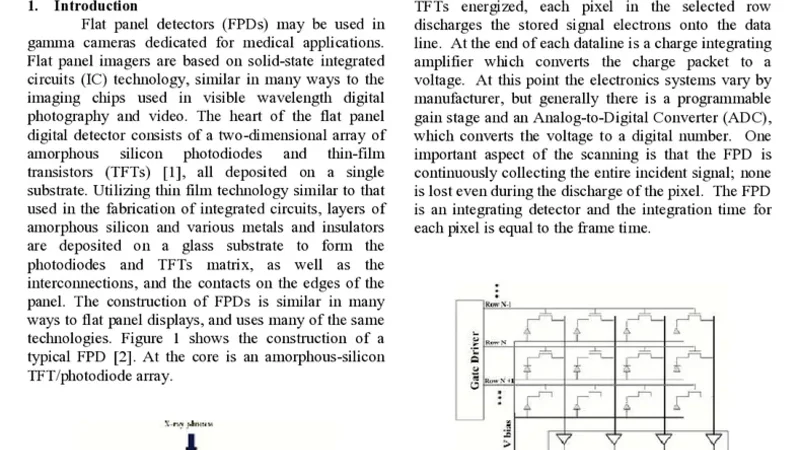

본 연구는 평판 검출기(FPD)용 TFT 배열에 전류미러 회로를 통합함으로써 기존 전압‑기반 읽기 방식이 갖는 몇 가지 근본적인 한계를 극복하고자 한다. 전류미러는 동일한 전류를 복제·분배하는 특성 덕분에 다중 픽셀의 신호를 하나의 공통 노드에 집합시킬 수 있다. 이는 전통적인 스위치 매트릭스에서 각 픽셀마다 별도의 선택 트랜지스터가 필요하던 구조와 달리, 스위치 수를 크게 감소시켜 회로 면적을 절감하고 레이아웃 복잡성을 낮춘다. 또한 전류 기반 읽기는 전압 기반에 비해 캐패시턴스에 의한 충전·방전 지연이 적어 변환 시간이 짧아진다. 논문에서는 4×4 배열을 시제품으로 제작했으며, 각 픽셀은 얇은막 트랜지스터(TFT)와 전류미러 소자로 구성된다. 전류미러는 MOSFET을 이용한 간단한 구조로, 입력 전류를 복제해 출력 트랜지스터에 전달한다. 이때 출력 트랜지스터는 고정된 전류값을 유지하도록 바이어스가 설계되어, 픽셀당 발생하는 광전류를 정확히 반영한다. 중요한 점은 동일 노드에 연결된 16개의 픽셀 전류가 물리적으로 합산되어 아날로그 신호로 출력된다는 것이다. 이를 통해 인접 픽셀의 광강도를 합산하는 ‘픽셀 블록 합성’이 가능해지며, 저조도 환경에서 신호‑대‑노이즈 비(SNR)를 향상시킬 수 있다. 또한, 전류미러 회로는 온도 변화에 대한 민감도가 낮아, 장시간 동작 시 안정적인 출력 특성을 제공한다. 제작 과정에서는 기존 a‑Si 기반 TFT 공정에 최소한의 추가 공정만을 적용했으며, 전류미러 트랜지스터는 동일한 공정 파라미터로 구현되어 제조 비용 상승을 억제하였다. 테스트 결과, 각 픽셀의 전류‑광 변환 특성이 일관되었으며, 16픽셀 합산 신호는 기대값과 근접한 선형성을 보였다. 그러나 전류미러의 복제 정확도는 트랜지스터 매칭에 크게 의존하므로, 대규모 배열로 확장할 경우 매칭 오차가 누적될 가능성이 있다. 또한, 전류 합산 과정에서 발생할 수 있는 포화 현상을 방지하기 위해 출력 버퍼 설계가 필요하다. 향후 연구에서는 매칭 보정 회로와 자동 캘리브레이션 알고리즘을 도입해 대형 64×64 혹은 그 이상의 매트릭스로 확장하는 방안을 모색하고 있다. 전반적으로 전류미러 기반 TFT 배열은 스위치 수 감소, 빠른 변환, 픽셀 블록 합성 등 다수의 장점을 제공하며, 차세대 고해상도 FPD 및 의료 영상 시스템에 적용될 잠재력이 크다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...