재귀형 이중크기 고정정밀도 연산

초록

본 논문은 2의 거듭제곱 크기를 갖는 정수에 대해 재귀적으로 두 개의 절반 크기 정수로 표현하는 “RecInt” 구조를 제안한다. C++ 템플릿 기반 구현을 통해 소형 정수는 머신 워드 연산을 사용하고, 큰 정수는 재귀적으로 고속 연산을 수행한다. 소프트웨어 성능은 GMP와 견줄 만하며, FPGA 구현을 위한 VHDL 자동 변환 가능성을 보인다.

상세 분석

RecInt은 k > k₀인 경우 2ᵏ 비트 정수를 두 개의 2ᵏ⁻¹ 비트 정수(High와 Low)로 나누어 저장한다. k₀는 목표 아키텍처에 따라 결정되며, 일반적인 32‑bit·64‑bit 환경에서는 k₀ = 5·6 정도가 적절하다. 이 설계는 C++ 템플릿과 부분 특수화를 활용해, 작은 k에 대해서는 기존 머신 워드(limb) 타입을 그대로 사용하고, 큰 k에 대해서는 재귀적 데이터 구조와 연산을 자동 생성한다.

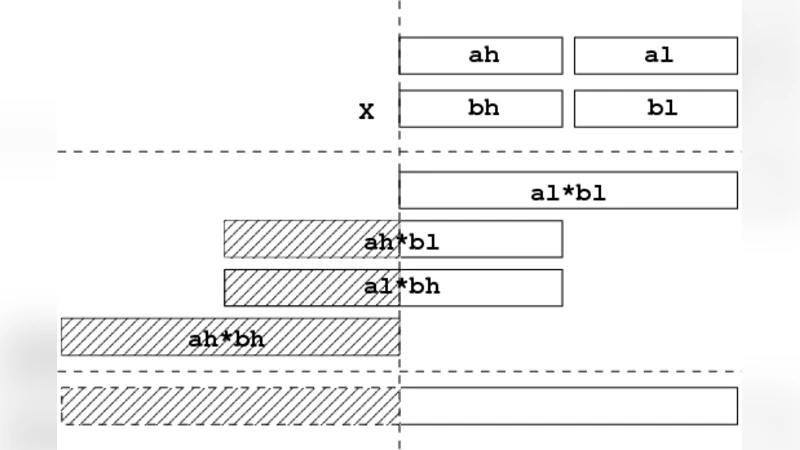

연산 측면에서 저자는 덧셈·뺄셈·곱셈·제곱·몫·나머지 등 기본 연산을 모두 구현했으며, 특히 “truncated multiplication”(상위 비트를 버리는 곱셈)과 “Montgomery reduction”(몫 없이 모듈러 곱을 수행)에서 재귀적 구조의 장점을 강조한다. 예를 들어, k 단계의 truncated multiplication은 1개의 완전 곱셈과 2개의 k‑1 단계 truncated multiplication만 필요하므로, 전통적인 4‑곱 방식보다 연산량이 크게 감소한다.

또한, Burnikel‑Ziegler 방식의 재귀적 나눗셈을 채택해 O(rs log 3 − 1 + r log s) 복잡도를 달성한다. 이는 큰 정수에 대한 유클리드 알고리즘과 확장 유클리드 알고리즘을 효율적으로 구현할 수 있게 한다.

소프트웨어 측면에서는 GMP의 어셈블리 루틴(예: mul_ppmm)을 재사용해 저수준 연산을 가속화하고, RecInt 구조 위에 고수준 연산을 레이어링한다. 벤치마크 결과는 고정 정밀도 연산에서 GMP와 동등하거나 소규모(≤256 bit)에서는 약간 앞서는 성능을 보인다.

하드웨어 구현에서는 C++ 코드를 GAUT라는 고수준 합성 툴을 통해 VHDL로 자동 변환한다. 초기 실험에서는 128 bit, 256 bit, 512 bit 모듈러 지수 연산을 Virtex‑5 FPGA에 매핑했으며, 파이프라인 깊이와 레지스터 사용량을 조절해 면적과 속도 간 트레이드오프를 확인했다. 현재 변환된 VHDL는 최적화되지 않았지만, 구조가 단순하고 재귀적이므로 향후 고성능 하드웨어 구현에 유리한 기반을 제공한다.

전체적으로 RecInt은 소프트웨어와 하드웨어 양쪽에서 재귀적 데이터 구조를 활용해 고정 정밀도 연산을 일관되게 구현할 수 있는 프레임워크이며, 특히 보안 암호 모듈(RSA, ECC)에서 요구되는 대규모 정수 연산을 효율적으로 지원한다는 점이 큰 강점이다.

댓글 및 학술 토론

Loading comments...

의견 남기기