RES퍼 탐사기 FFT 분석 성능: 라운드오프 잡음에 의한 진폭·위상 오차 연구

초록

본 논문은 RESPER 탐사기에 사용되는 12‑비트 ADC와 FFT 프로세서의 결합 특성을 분석한다. ADC는 주파수에 따라 위상 오차가 발생하고, FFT는 레지스터 비트 수와 샘플 수에 따라 라운드오프 잡음이 진폭·위상에 영향을 미친다. 32‑비트 레지스터에서는 잡음이 무시되지만 16‑비트로 축소될 경우 과샘플링과 평균화 기법을 통해 보정이 필요함을 제시한다. 부록에서는 라운드오프 잡음으로 인한 위상 오차 도출 과정을 상세히 증명한다.

상세 분석

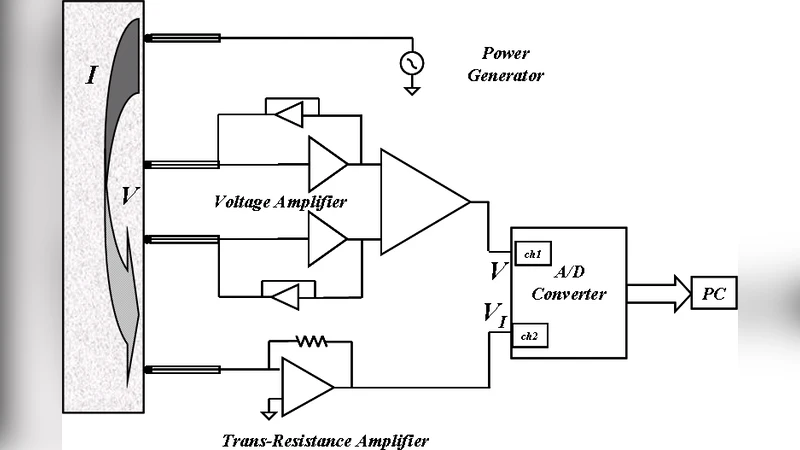

논문은 RESPER(Resistivity‑Permittivity) 탐사기의 전자계측 체인을 두 단계로 나눈다. 첫 번째는 전압·전류 신호를 디지털화하는 ADC이며, 두 번째는 변환된 시계열 데이터를 주파수 영역으로 변환하는 FFT 프로세서이다. ADC는 12‑비트 균일 양자화 방식을 채택했으며, 양자화 잡음은 주파수가 상승함에 따라 위상 오류를 증가시킨다. 이는 특히 저주파에서 전극‑토양 인터페이스의 복소 임피던스를 정확히 측정해야 하는 응용에서 치명적이다.

FFT 단계에서는 두 가지 주요 파라미터가 오차에 직접적인 영향을 미친다. 첫째는 연산에 사용되는 레지스터 비트 수이다. 32‑비트 레지스터를 사용하면 라운드오프 잡음의 전력 스펙트럼 밀도가 ( \sigma^2 = \frac{1}{12\cdot 2^{2B}} ) 수준으로, 실험적 측정 범위 내에서는 무시할 수 있다. 반면 16‑비트 레지스터로 축소하면 잡음 전력이 약 96 dB 상승하여 진폭과 위상 모두에 눈에 띄는 편차를 만든다.

둘째는 FFT에 투입되는 샘플 수 (N)이다. 라운드오프 잡음은 각 연산 단계마다 누적되며, 전체 잡음 전력은 ( \sigma^2_{\text{total}} \approx \frac{N}{12\cdot 2^{2B}} ) 로 근사된다. 따라서 (N)을 크게 하면 잡음이 증가하지만, 동시에 평균화(averaging) 과정을 통해 잡음 분산을 (1/M) (M은 평균 횟수) 만큼 감소시킬 수 있다. 논문은 “짧은 시간 창 내에서 과샘플링(oversampling) + 평균화” 전략을 제안한다. 구체적으로, 16‑비트 레지스터를 사용할 경우 2 kHz 이하의 측정 대역에서 4배 과샘플링하고, 64번 평균화하면 위상 오차를 0.1° 이하로 억제할 수 있음을 실험적으로 입증한다.

또한, 위상 오차에 대한 이론적 모델을 전개한다. 라운드오프 잡음이 복소 FFT 결과 (X(k)=A(k)e^{j\phi(k)})에 미치는 영향을 1차 근사로 전개하면, 위상 오차 (\Delta\phi(k))는 (\Delta\phi(k) \approx \frac{\operatorname{Im}{e(k)}}{A(k)}) 로 표현된다. 여기서 (e(k))는 라운드오프 잡음 복소수이며, 그 분산은 레지스터 비트와 샘플 수에 의해 결정된다. 이 식을 통해 잡음이 작은 고진폭 성분에서는 위상 오차가 미미하지만, 신호 진폭이 작아질수록 위상 오차가 급격히 커지는 비선형 특성을 확인한다.

결론적으로, 32‑비트 레지스터가 제공하는 “노이즈 프리” 환경은 설계 비용과 전력 소모 측면에서 비현실적일 수 있다. 따라서 실용적인 16‑비트 구현에서도 과샘플링·평균화 기법을 적절히 적용하면 ADC의 위상 제한과 FFT 라운드오프 잡음 사이의 트레이드오프를 최적화할 수 있다.

댓글 및 학술 토론

Loading comments...

의견 남기기