완전 비동기식 스파스 선형 시스템 해결을 위한 지시 전송 방식

초록

본 논문은 대칭 양정( SPD) 스파스 선형 시스템을 풀기 위해, 통신 지연을 직접 모델링한 ‘지시 전송 라인(Directed Transmission Line, DTL)’을 도입한 완전 비동기식 연속시간 반복 알고리즘인 Directed Transmission Method(DTM)를 제안한다. 전기 그래프와 전기 정점 분할(Electric Vertex Splitting, EVS)을 이용해 문제를 서브그래프로 나눈 뒤, 각 서브그래프 사이에 DTL 쌍을 삽입해 알고리즘‑아키텍처 지연 매핑을 구현한다. 라플라스 변환의 최종값 정리를 이용해 수렴성을 증명하고, 수치 실험을 통해 안정성과 효율성을 확인하였다.

상세 분석

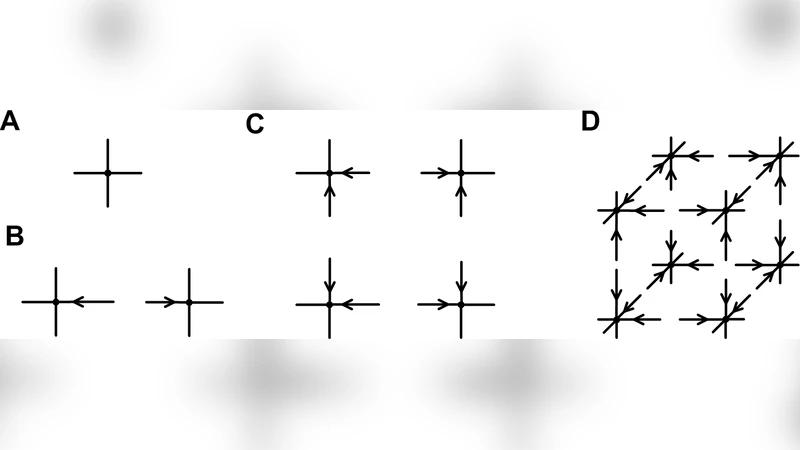

DTM은 기존 비동기 블록‑Jacobi나 비동기 Schwarz 계열이 갖는 동기화 오버헤드와 수렴 속도 저하 문제를 근본적으로 해소하려는 시도이다. 핵심 아이디어는 ‘전송 라인’이라는 물리적 개념을 알고리즘 수준에서 추상화해, 각 프로세서 간의 실제 통신 지연을 그대로 수식에 반영하는 것이다. 이를 위해 저자들은 Directed Transmission Line(DTL)이라는 가상의 회로 요소를 정의하고, 입력‑출력 전압·전류 관계를 U_out(t)=U_in(t−τ)−Z·I_out(t) 와 같은 연속시간 지연 방정식(2.1)으로 기술한다. DTL은 방향성을 갖기 때문에 τ₁₂ 와 τ₂₁ 가 다를 수 있으며, 이는 비대칭 네트워크 환경(예: 서로 다른 네트워크 대역폭·지연)에서도 정확히 매핑된다.

전기 그래프(e‑graph) 개념을 도입해 선형 시스템을 전기 회로 형태로 변환하고, 전기 정점 분할(EVS)으로 경계 정점을 쌍으로 복제한다. 각 복제된 정점은 ‘포트’가 되며, 포트 사이에 DTL 쌍(DTLP)을 삽입한다. 이렇게 구성된 서브그래프는 독립적인 로컬 시스템(식 5.9)으로 변환되며, 로컬 시스템의 계수 행렬은 고정된 SPD 행렬이므로 한 번의 Cholesky 분해만으로 반복 계산을 가볍게 수행할 수 있다.

연속시간 반복식(5.7‑5.9)은 전송 지연 τ와 특성 임피던스 Z를 매개변수로 갖는다. 특성 임피던스는 수렴 속도에 직접적인 영향을 미치며, 적절히 조정하면 DTM의 수렴을 크게 가속화할 수 있다(그림 9). 수렴성 증명은 라플라스 변환 후 최종값 정리를 적용해, 모든 τ가 양수이고 Z가 양의 대각 행렬인 경우 전역 시스템이 안정적인 고정점에 수렴함을 보인다.

DTM의 장점은 다음과 같다. 첫째, 전역 동기화가 전혀 필요 없으며, 각 프로세서는 로컬 시스템을 독립적으로 풀고, 인접 서브그래프에서 전달된 최신 상태만 받아 업데이트한다. 둘째, 통신 지연을 정확히 모델링하므로, 실제 하드웨어 지연이 큰 이질적 클러스터에서도 효율적으로 동작한다. 셋째, 로컬 시스템 행렬이 변하지 않으므로 사전 팩터링을 활용해 연산 비용을 크게 절감한다.

하지만 몇 가지 한계도 존재한다. 현재 이론은 SPD 행렬에만 적용 가능하므로, 비대칭 혹은 비정정(Indefinite) 시스템에는 확장하기 어렵다. 또한 τ와 Z의 선택이 수렴에 민감한데, 최적 파라미터를 자동으로 찾는 방법이 제시되지 않았다. 구현 측면에서는 전기 그래프와 EVS를 자동으로 생성하고, DTL 쌍을 매핑하는 복잡한 전처리 단계가 필요하다. 마지막으로, 연속시간 모델을 실제 디지털 시스템에 적용할 때는 시간 스텝화 혹은 샘플링 오류가 발생할 수 있어, 수치 안정성에 대한 추가 검증이 요구된다.

전반적으로 DTM은 비동기 병렬 선형 솔버 설계에 새로운 패러다임을 제시하며, 특히 통신 지연이 큰 대규모 이기종 클러스터에서 유망한 접근법으로 평가된다.

댓글 및 학술 토론

Loading comments...

의견 남기기