시간 영역을 활용한 PCB 전원 무결성 분석

초록

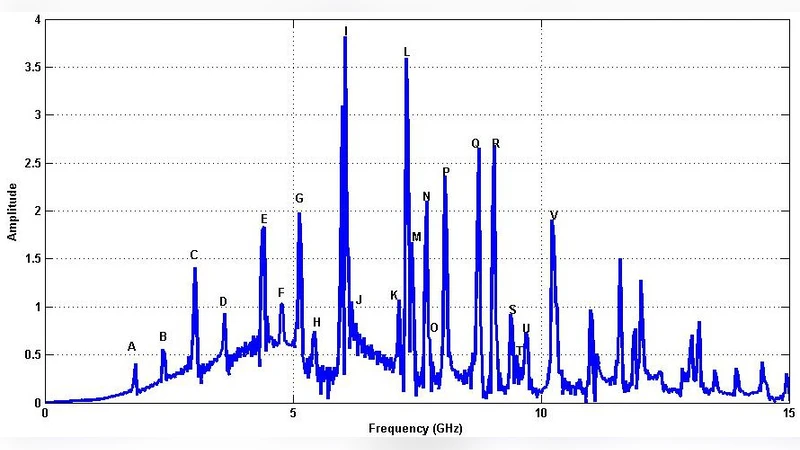

본 논문은 유한 차분 시간 영역(FDTD) 방법을 이용해 PCB 전원·접지 평면의 전자기 파동 전파와 공진 현상을 시뮬레이션한다. 완전 매칭 층(PML)으로 경계 반사를 억제하고, 펄스 전류가 발생시킨 전기장 파동이 평면 전체에 복합적인 간섭 패턴을 형성하며, 이러한 공진 파동이 장시간 지속함을 확인한다. FFT 분석을 통해 PCB를 전기·자기 경계가 있는 공진 공동으로 모델링할 수 있음을 입증한다.

상세 분석

이 연구는 전력 무결성(Power Integrity, PI) 문제를 전자기 파동의 시간적 전개 관점에서 접근한다는 점에서 의미가 크다. 전통적으로 PI는 주파수 영역에서 임피던스와 전압 강하를 분석했지만, 급격한 전류 스파이크가 발생하는 현대 고속 디지털 회로에서는 순간적인 전자기 파동이 PCB 전체에 퍼져 복합적인 반사와 간섭을 일으킨다. 저자는 3‑D FDTD 방정식을 이용해 전원·접지 평면을 격자화하고, 유니액셜 PML을 적용해 인공 경계에서의 반사를 최소화함으로써 실제 PCB 내부에서 파동이 어떻게 전파되는지를 시간에 따라 정확히 포착한다. 시뮬레이션 결과, 펄스가 전원 평면을 따라 전파될 때 소스와 반사 파동 사이에 1차 간섭 패턴이 형성되고, 이후 다중 반사에 의해 복잡한 스탠다드 모드가 발생한다. 이러한 모드는 전압 변동을 일으켜 보드 상 모든 부품에 영향을 미칠 수 있다. 특히, FFT 분석을 통해 도출된 공진 주파수는 PCB를 두 개의 전기 경계(전원·접지)와 네 개의 자기 경계(에지)로 이루어진 직육면체 공동으로 모델링했을 때 기대되는 고유 주파수와 일치한다는 점이 주목할 만하다. 이는 PCB 설계 시 물리적 치수와 재료 유전율을 고려한 공진 분석이 필요함을 시사한다. 또한, 파동이 수십 나노초에서 마이크로초 수준까지 지속되는 현상은 전원 레귤레이터와 디지털 로직 사이의 타이밍 마진을 감소시킬 위험이 있다. 따라서 설계자는 전원 레이어와 접지 레이어의 배치, 스루홀 및 비아 위치, 그리고 전원 인덕턴스 최소화를 위한 레이아웃 최적화를 통해 이러한 파동을 억제해야 한다. 마지막으로, 본 연구는 FDTD 기반 시뮬레이션이 전력 무결성 분석에 실시간 파동 시각화와 정량적 공진 주파수 추출을 제공함으로써, 기존 주파수 영역 해석을 보완하는 강력한 도구가 될 수 있음을 보여준다.

댓글 및 학술 토론

Loading comments...

의견 남기기