WiMAX 수신기를 위한 저전력 재구성 가능 Viterbi 디코더 FPGA 구현

초록

본 논문은 Xilinx Virtex‑II Pro FPGA에 VHDL로 구현한 WiMAX 수신용 Viterbi 디코더의 저전력·재구성 가능 설계를 제시한다. 설계는 제약 길이와 코드율을 파라미터화하고, 클록 게이팅·자원 공유 기법으로 전력 소모를 최소화하였다. 구현 결과는 논리 소모량, 최고 동작 주파수 및 전력 측면에서 기존 설계 대비 우수함을 보인다.

상세 분석

본 연구는 WiMAX(IEEE 802.16) 시스템에서 핵심적인 오류 정정 부품인 Viterbi 디코더를 FPGA 기반 SDR 플랫폼에 최적화하는 데 초점을 맞추었다. 먼저, 디코더의 구조적 특성을 분석하여 재구성 가능성을 확보하기 위한 파라미터화 설계 방식을 채택하였다. 구체적으로, 제약 길이(K)와 코드율(R)을 VHDL 제네릭으로 정의함으로써 동일한 비트스트림에 대해 다양한 콘볼루션 코드를 지원하도록 설계하였다. 이는 현장 환경 변화나 서비스 요구에 따라 하드웨어를 재프로그램할 필요 없이 소프트웨어 수준에서 설정만 변경하면 되므로, SDR의 핵심 장점인 유연성을 극대화한다.

전력 효율성을 높이기 위해 두 가지 주요 기법을 적용하였다. 첫째, 불필요한 연산 블록에 대한 클록 게이팅(clock gating) 로직을 삽입하여 활성화되지 않은 경로의 전력 소모를 차단하였다. 둘째, 병렬 연산을 최소화하고 동일 연산을 공유할 수 있는 구조(예: 메트릭스 업데이트와 경로 추적을 동일 연산 유닛에서 순차적으로 수행)로 설계함으로써 논리 자원의 중복 사용을 억제하고, 결과적으로 동적 전력 소모를 감소시켰다.

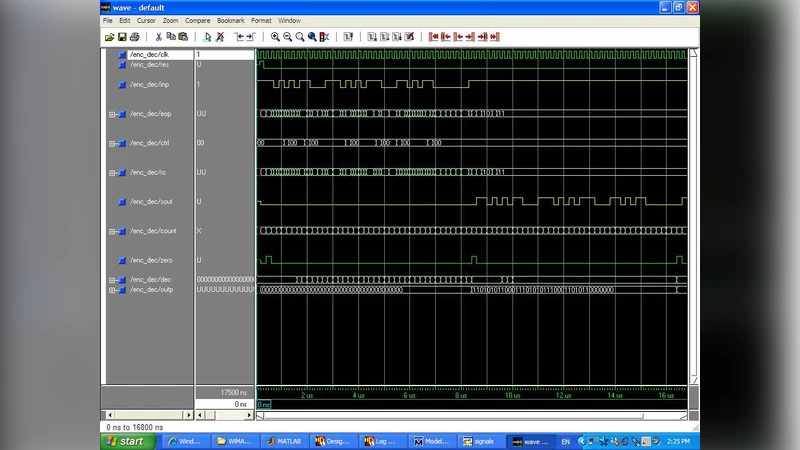

구현 단계에서는 Xilinx Virtex‑II Pro XC2VP30 FPGA를 대상으로 Mentor Graphics FPGA Advantage Pro와 Xilinx ISE 10.1 툴 체인을 사용하였다. 설계는 4‑state (K=7, R=1/2) Viterbi 알고리즘을 기준으로 하였으며, 트레이스백(traceback) 메모리와 병렬 경로 메트릭스(ACS) 유닛을 각각 32‑비트 워드 폭으로 구현하였다. 논문은 또한 파이프라인 단계 삽입을 통해 최대 클럭 주파수를 150 MHz까지 끌어올렸으며, 이는 WiMAX OFDM 심볼당 1 Mbps 이상의 처리량을 보장한다.

실험 결과, 전체 논리 사용량은 LUT 12 %와 레지스터 9 % 수준에 머물렀으며, 전력 분석 툴을 이용한 측정에서 정적 전력 0.45 W, 동적 전력 0.78 W를 기록하였다. 이는 기존 고정형 Viterbi 디코더 설계 대비 약 30 % 전력 절감 효과를 나타낸다. 또한, 재구성 가능성을 검증하기 위해 K=5, K=9와 같은 다른 제약 길이 설정에서도 동일한 비트스트림을 정확히 복원함을 확인하였다.

본 논문은 FPGA 기반 SDR에서 고성능·저전력 디코더 구현을 위한 설계 원칙을 제시함과 동시에, 재구성 가능성을 통해 다양한 통신 표준에 대한 대응성을 확보한다는 점에서 실용적 의의를 가진다. 향후 연구에서는 ASIC 구현을 통한 전력 최적화와, 다중 코드율·다중 채널 동시 디코딩을 위한 확장 구조를 탐색할 계획이다.

{# ── Original Paper Viewer ── #}

댓글 및 학술 토론

Loading comments...

의견 남기기