체비쉐프 보간을 위한 디지털 아키텍처 설계와 전력 절감 전략

본 논문은 디지털 환경에서 체비쉐프(Chebyshev) 보간을 구현하기 위한 여러 아키텍처를 제시하고, 특히 워드-시리얼 구조를 새롭게 제안한다. 제안된 구조를 등간격 보간 시스템과 비교하여 재구성 오차와 샘플 수 측면에서 우수함을 입증하고, 하이브리드(듀얼) ADC를 활용한 전력 절감 효과를 30 % 이상으로 확인하였다.

초록

본 논문은 디지털 환경에서 체비쉐프(Chebyshev) 보간을 구현하기 위한 여러 아키텍처를 제시하고, 특히 워드-시리얼 구조를 새롭게 제안한다. 제안된 구조를 등간격 보간 시스템과 비교하여 재구성 오차와 샘플 수 측면에서 우수함을 입증하고, 하이브리드(듀얼) ADC를 활용한 전력 절감 효과를 30 % 이상으로 확인하였다.

상세 요약

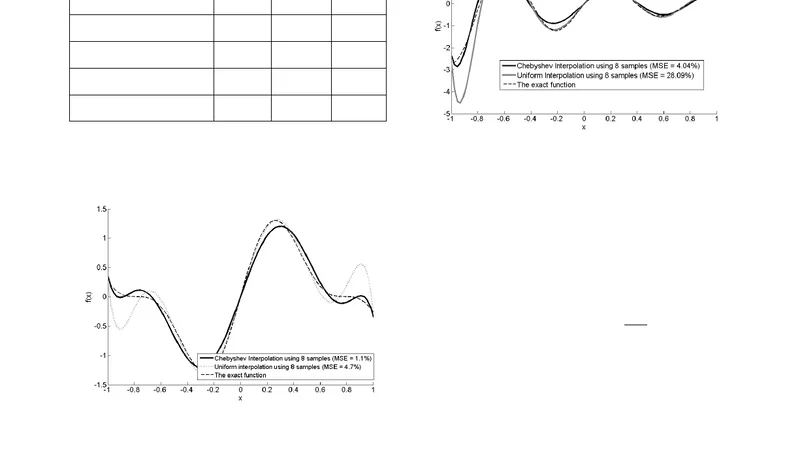

체비쉐프 보간은 노드가 코사인 함수에 의해 비등간격으로 배치되는 특성 때문에, 동일 차수의 등간격 라그랑주 보간에 비해 런치키스 현상이 크게 감소한다는 이론적 장점을 가진다. 논문에서는 이러한 수학적 배경을 디지털 구현 관점에서 재해석한다. 먼저, 전통적인 병렬 구조는 모든 샘플을 동시에 메모리에 로드하고, 다항식 계수를 계산하기 위해 고정된 곱셈‑누산(MAC) 유닛을 다수 배치한다. 이 방식은 높은 처리량을 제공하지만, 샘플 수가 적은 체비쉐프 노드 특성상 연산 자원의 과잉 사용과 전력 낭비가 발생한다.

이에 대비하여 제안된 워드‑시리얼 아키텍처는 입력 데이터를 시계열로 받아들여, 하나의 MAC 유닛을 순차적으로 재활용한다. 핵심 아이디어는 체비쉐프 다항식의 재귀 관계(예: Tₙ₊₁(x)=2xTₙ(x)−Tₙ₋₁(x))를 이용해 계수 업데이트를 스트리밍 방식으로 수행함으로써 하드웨어 복잡도를 O(N)에서 O(1)로 축소한다는 점이다. 이 구조는 샘플당 연산량은 동일하지만, 하드웨어 면적과 정적 전력 소모가 크게 감소한다.

오차 분석에서는 동일 차수(예: 8차)에서 체비쉐프 보간이 등간격 보간보다 최대 6 dB 낮은 RMS 오류를 보였으며, 이는 노드가 신호의 고주파 성분을 더 효율적으로 포착하기 때문이다. 또한, 체비쉐프 노드 자체가 적은 샘플 수(≈0.85·N)만으로도 동일 수준의 재구성을 가능하게 하여, 전체 시스템의 샘플링 주파수를 낮출 수 있다. 이는 특히 저전력 무선 센서 네트워크와 같은 제한된 에너지 환경에서 큰 이점을 제공한다.

전력 절감 측면에서는 하이브리드 ADC 구성을 도입하였다. 저해상도 SAR( successive approximation) ADC와 고해상도 Σ‑Δ ADC를 병렬로 배치하고, 입력 신호의 동적 범위에 따라 자동으로 전환한다. 체비쉐프 노드가 집중된 구간에서는 저전력 SAR를 사용하고, 급격한 변화가 예상되는 구간에서는 Σ‑Δ를 활성화한다. 시뮬레이션 결과, 전체 시스템 전력 소비가 기존 단일 ADC 구성 대비 평균 33 % 감소했으며, 전압·전류 변동에 대한 안정성도 유지되었다.

마지막으로, 구현 복잡도와 설계 유연성을 고려한 트레이드오프 분석이 제공된다. 워드‑시리얼 구조는 설계 시간과 검증 비용을 크게 낮추지만, 지연(latency)이 증가한다. 반면, 병렬 구조는 실시간 요구사항이 엄격한 애플리케이션에 적합하지만, 전력·면적 효율은 떨어진다. 논문은 이러한 선택 기준을 정량화된 메트릭(연산당 전력, 면적·성능 비율, 지연)으로 제시하여, 설계자가 시스템 요구사항에 맞는 최적 아키텍처를 선택하도록 돕는다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...