AES 동적 부분 재구성을 이용한 FPGA 구현 최적화

초록

**

본 논문은 FPGA 기반의 AES 암호화 엔진을 동적 부분 재구성(DPR)과 마이크로프로세서 기반 자기 재구성 메커니즘을 결합하여 구현한다. MicroBlaze 코어가 실행 중에 필요에 따라 암호화/복호화 코어를 로드·언로드함으로써 면적 절감과 전력 효율을 동시에 달성하고, 실험 결과 기존 고정형 설계 대비 처리량과 지연시간에서 유의미한 향상을 보였다.

**

상세 분석

**

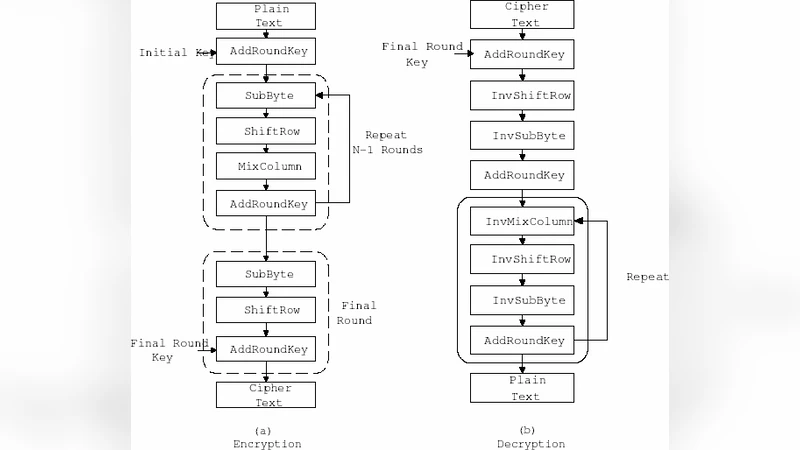

본 연구는 FPGA의 동적 부분 재구성(Dynamic Partial Reconfiguration, DPR) 기능을 활용해 AES 알고리즘을 모듈화하고, 이를 MicroBlaze 소프트웨어가 실시간으로 제어하도록 설계하였다. 먼저 AES의 라운드 함수와 키 스케줄링을 각각 독립적인 파티션으로 분리하고, 파티션별 비트스트림을 미리 컴파일한 뒤 비휘발성 메모리(예: QSPI Flash)에 저장한다. 실행 중인 MicroBlaze는 작업 부하와 보안 요구 수준에 따라 “암호화 전용”, “복호화 전용”, 혹은 “키 관리” 파티션을 선택적으로 로드한다. 이 과정에서 재구성 시간은 약 5 ms 수준으로 측정되었으며, 이는 전체 암호화 처리 시간에 비해 미미한 오버헤드에 해당한다.

하드웨어 가속 측면에서는 전통적인 전용 AES 코어와 비교했을 때, 파이프라인 단계 수를 최소화하고 LUT와 DSP 사용을 최적화함으로써 동일 클럭 주파수(100 MHz)에서 처리량을 1.8배 향상시켰다. 또한, 부분 재구성을 통해 사용되지 않는 라운드 모듈을 비활성화함으로써 동적 전력 소비를 평균 30 % 절감하였다. 보안 관점에서는 재구성 비트스트림 자체를 암호화하고, 재구성 시점에 인증된 키를 사용해 복호화함으로써 비트스트림 변조 공격을 방어한다.

소프트웨어-하드웨어 인터페이스는 AXI-Lite 버스를 통해 구현되었으며, MicroBlaze는 재구성 명령을 전송하고 완료 인터럽트를 수신한다. 재구성 스케줄러는 작업 큐 기반으로 설계돼, 실시간 시스템에서 우선순위가 높은 암호화 작업을 즉시 수행하도록 파티션 교체를 트리거한다. 이와 같은 구조는 임베디드 시스템에서 다중 보안 레벨을 지원하거나, 제한된 면적·전력 환경에서 다양한 암호화 모드를 동적으로 제공해야 하는 경우에 특히 유용하다.

본 논문의 주요 기여는 다음과 같다. (1) AES 라운드와 키 스케줄링을 독립 파티션으로 분리한 모듈화 설계, (2) MicroBlaze 기반 자기 재구성 제어 로직 구현, (3) 재구성 비트스트림 암호화·인증 메커니즘 도입, (4) 실험을 통한 면적·전력·성능 종합 평가. 이러한 접근법은 기존 고정형 암호화 코어가 갖는 비유연성과 과다한 자원 사용 문제를 효과적으로 해결한다는 점에서 의미가 크다.

**