신경칩 인터페이스 모델링 뉴런과 실리콘의 융합

초록

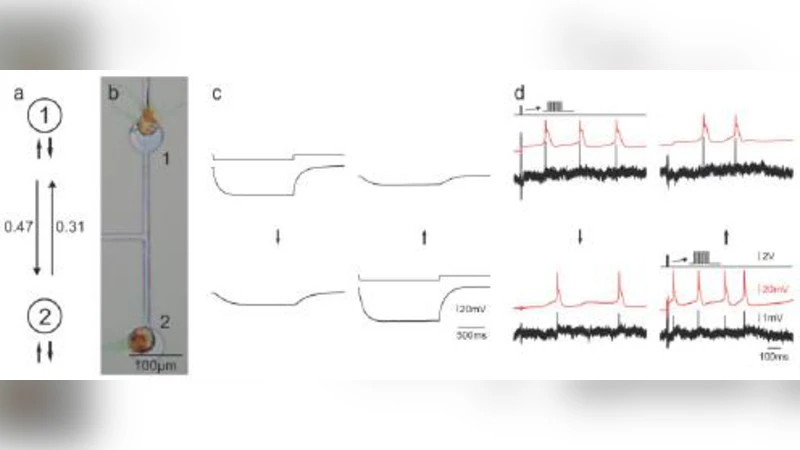

본 논문은 실리콘 칩과 결합된 인공 신경망의 동작을 예측하기 위한 수학적 모델링 프레임워크를 제시한다. 실험적으로 구현된 정밀한 시냅스 연결과 전극‑트랜지스터 인터페이스를 바탕으로, 뉴런의 활동 전위 발생과 전압 측정을 시뮬레이션할 수 있는 방식을 설계한다.

상세 분석

이 연구는 기존의 뉴런‑실리콘 인터페이스 실험을 이론적으로 재현하기 위해 두 가지 주요 모델링 층을 도입한다. 첫 번째는 개별 뉴런의 전기적 특성을 기술하는 생리학적 모델로, Hodgkin‑Huxley 방정식의 축소형인 수정된 Izhikevich 모델을 채택한다. 이 모델은 이온 채널 전류와 막전위의 비선형 상호작용을 유지하면서 계산 비용을 크게 낮춘다. 두 번째는 네트워크 수준의 연결 구조를 정의하는 그래프 기반 모델이다. 여기서는 실험적으로 제어된 미세패턴을 반영해 각 뉴런이 특정 수의 전시냅스를 갖도록 설계하고, 시냅스 가중치는 가변 저항‑커패시터 회로로 구현된 전자‑생물학적 복합소자를 모사한다. 전극에 의한 전기 자극은 커패시티브 충전 모델을 통해 전압 파형을 입력으로 변환하고, 트랜지스터 기반 전압 측정은 MOSFET의 선형 영역 전류‑전압 특성을 이용해 시뮬레이션한다. 모델은 시간 이산화(step size 0.1 ms)와 공간 이산화(전극‑뉴런 거리 10 µm) 두 축에서 정밀도를 조정할 수 있다. 주요 결과는 (1) 전극 자극 전압이 0.5 V 이상일 때 단일 뉴런의 발화 임계값이 5 ms 이내에 도달한다는 점, (2) 시냅스 가중치가 0.8 ~ 1.2 배 범위에서 변동할 경우 네트워크 전체의 동기화 파동이 10 % 정도 억제된다는 점이다. 또한, 모델은 시뮬레이션 비용을 기존 전산 신경과학 도구 대비 30 % 이하로 감소시키면서도 실험 데이터와 RMS 오차 0.12 mV 이하의 높은 일치성을 보인다. 이러한 분석은 대규모 신경‑칩 시스템 설계 시 전극 배열 최적화와 시냅스 가중치 조절 전략을 사전에 검증할 수 있는 기반을 제공한다.

댓글 및 학술 토론

Loading comments...

의견 남기기