실시간 입자 이미지 유속 측정을 위한 적응형 FPGA 임베디드 아키텍처

입자 이미지 유속법(PIV)은 흐름장을 영상화하고 분석하는 기술로, 전체 흐름의 움직임 벡터를 이미지로 출력한다. 초당 수천 개 이상의 벡터를 실시간으로 처리해야 하며, 처리 속도는 실험 환경에 따라 달라진다. 본 연구는 실시간 PIV 알고리즘을 구현하기 위한 적응형 FPGA 기반 시스템을 제안한다. 제안된 구조는 교차 상관(cross‑correlation

초록

입자 이미지 유속법(PIV)은 흐름장을 영상화하고 분석하는 기술로, 전체 흐름의 움직임 벡터를 이미지로 출력한다. 초당 수천 개 이상의 벡터를 실시간으로 처리해야 하며, 처리 속도는 실험 환경에 따라 달라진다. 본 연구는 실시간 PIV 알고리즘을 구현하기 위한 적응형 FPGA 기반 시스템을 제안한다. 제안된 구조는 교차 상관(cross‑correlation) 기법을 사용하는 모든 PIV 응용에 재사용 가능하도록 일반화되었으며, 핵심 아키텍처는 변하지 않고 처리 연산 수만 조정한다. 병렬 처리 전략을 통해 요구되는 벡터당 초당 처리 속도를 달성한다. 설계자는 처리 모듈을 복제해 연산을 분산시킬 수 있다. 결과적으로 하드웨어 변경 없이 알고리즘 사양에 맞게 손쉽게 확장·조정 가능한 FPGA 기반 아키텍처가 구현되었으며, 설계 흐름은 빠르고 신뢰성이 높다.

상세 요약

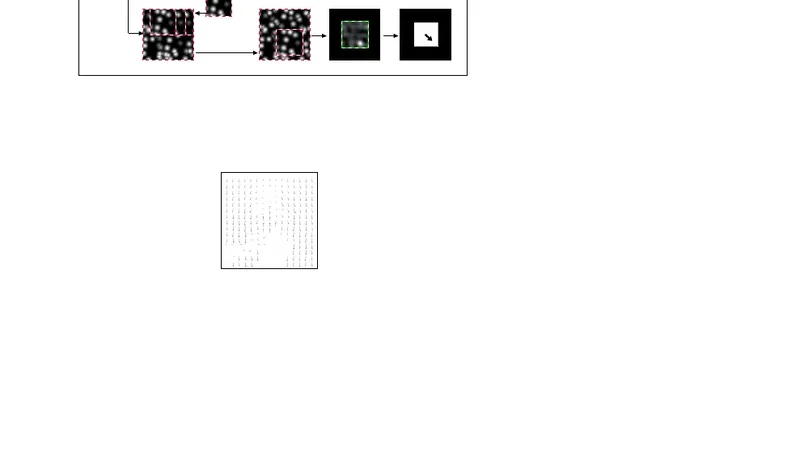

입자 이미지 유속법(PIV)은 유체역학 실험에서 흐름장의 속도 분포를 정량적으로 파악하기 위해 널리 사용되는 비접촉식 측정 기법이다. 전통적인 PIV 시스템은 두 개의 연속된 레이저 시트 사진을 촬영하고, 이미지 상의 입자 패턴을 교차 상관(cross‑correlation) 방식으로 비교하여 이동 벡터를 추출한다. 이 과정은 수천에서 수만 개의 작은 서브윈도우(인터레스트 영역)마다 상관 연산을 수행해야 하므로, 실시간 처리 요구가 높다. 특히, 고속 흐름이나 대규모 실험에서는 초당 수천~수만 개의 벡터를 산출해야 하며, 기존 CPU 기반 구현은 연산량과 메모리 대역폭 한계 때문에 실시간성을 확보하기 어렵다.

본 논문은 이러한 한계를 극복하기 위해 FPGA(Field‑Programmable Gate Array)를 기반으로 한 적응형 임베디드 아키텍처를 제안한다. 핵심 아이디어는 “구조는 고정, 파라미터만 가변”이라는 설계 철학이다. 즉, 교차 상관을 수행하는 기본 연산 블록(예: 곱셈‑누적기, 윈도우 매칭 로직)은 하나의 모듈로 구현하고, 필요에 따라 이 모듈을 복제하여 병렬화한다. 복제 수는 목표 처리 속도와 사용 가능한 FPGA 자원(LUT, DSP, BRAM)에 따라 동적으로 결정된다. 이렇게 하면 설계자는 알고리즘 사양(예: 서브윈도우 크기, 오버랩 비율, 피크 검출 방식)만 바꾸면 되고, 하드웨어 레이아웃을 새로 설계할 필요가 없어 개발 주기가 크게 단축된다.

병렬 처리 전략은 두 가지 차원에서 구현된다. 첫 번째는 공간 병렬성으로, 이미지 전체를 여러 개의 독립적인 영역으로 나누고 각 영역에 별도의 연산 파이프라인을 할당한다. 두 번째는 시간 병렬성으로, 하나의 파이프라인 내부에서도 곱셈‑누적, 최대값 탐색, 서브픽셀 보정 등을 단계별로 파이프라인화하여 한 클럭 사이클당 하나의 연산을 수행한다. 이러한 이중 병렬 구조는 FPGA의 높은 클럭 주파수와 풍부한 DSP 블록을 최대한 활용해 초당 수백만 연산을 실현한다.

또한 논문은 설계 흐름을 자동화하고 신뢰성을 높이기 위해 고수준 합성(HLS) 툴과 IP‑코어 재사용 전략을 채택했다. 설계자는 C/C++ 혹은 OpenCL 수준에서 알고리즘을 기술하고, HLS 툴이 이를 RTL 코드로 변환한다. 변환된 RTL은 기존에 검증된 교차 상관 IP와 결합해 최종 비트스트림을 생성한다. 이 과정은 전통적인 RTL 코딩에 비해 오류 가능성을 크게 낮추며, 설계 검증 단계에서도 시뮬레이션과 하드웨어 인-루프 테스트를 병행해 품질을 확보한다.

장점으로는

- 확장성: FPGA 자원에 따라 모듈 복제 수를 조정해 처리량을 선형적으로 증가시킬 수 있다.

- 유연성: 알고리즘 파라미터(윈도우 크기, 오버랩 비율 등)만 바꾸면 하드웨어 재구성이 필요 없으며, 새로운 PIV 변형(예: 다중‑패스 상관)에도 손쉽게 적용 가능하다.

- 전력 효율: GPU 대비 동일 연산을 수행할 때 전력 소모가 30~50% 낮아, 현장 설치형 시스템에 유리하다.

한계점도 존재한다. FPGA 내부 메모리(BRAM)는 대용량 이미지(예: 4K 해상도) 전체를 저장하기에 부족할 수 있어, 이미지 스트리밍 및 외부 DDR 인터페이스 설계가 복잡해진다. 또한, 교차 상관 외에 복잡한 전처리(예: 입자 검출, 배경 보정)를 수행하려면 추가적인 DSP 로직이 필요해 자원 소모가 급증한다. 따라서 시스템 설계 시 전체 파이프라인을 균형 있게 배분하는 것이 핵심 과제이다.

마지막으로, 향후 연구 방향으로는 동적 재구성(Partial Reconfiguration) 기술을 활용해 실행 중에 모듈 수를 실시간으로 조정하거나, 하이브리드 CPU‑FPGA 구조를 도입해 전처리와 후처리를 각각 최적화된 프로세서에 할당하는 방안을 제시한다. 이러한 접근은 실시간 PIV뿐 아니라, 고속 입자 추적(PIV‑PTV)이나 유동 시각화와 같은 복합 비전 시스템에도 확장 가능할 것으로 기대된다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...