저정밀 ADC를 활용한 트랜시버 설계: 정보이론적 관점

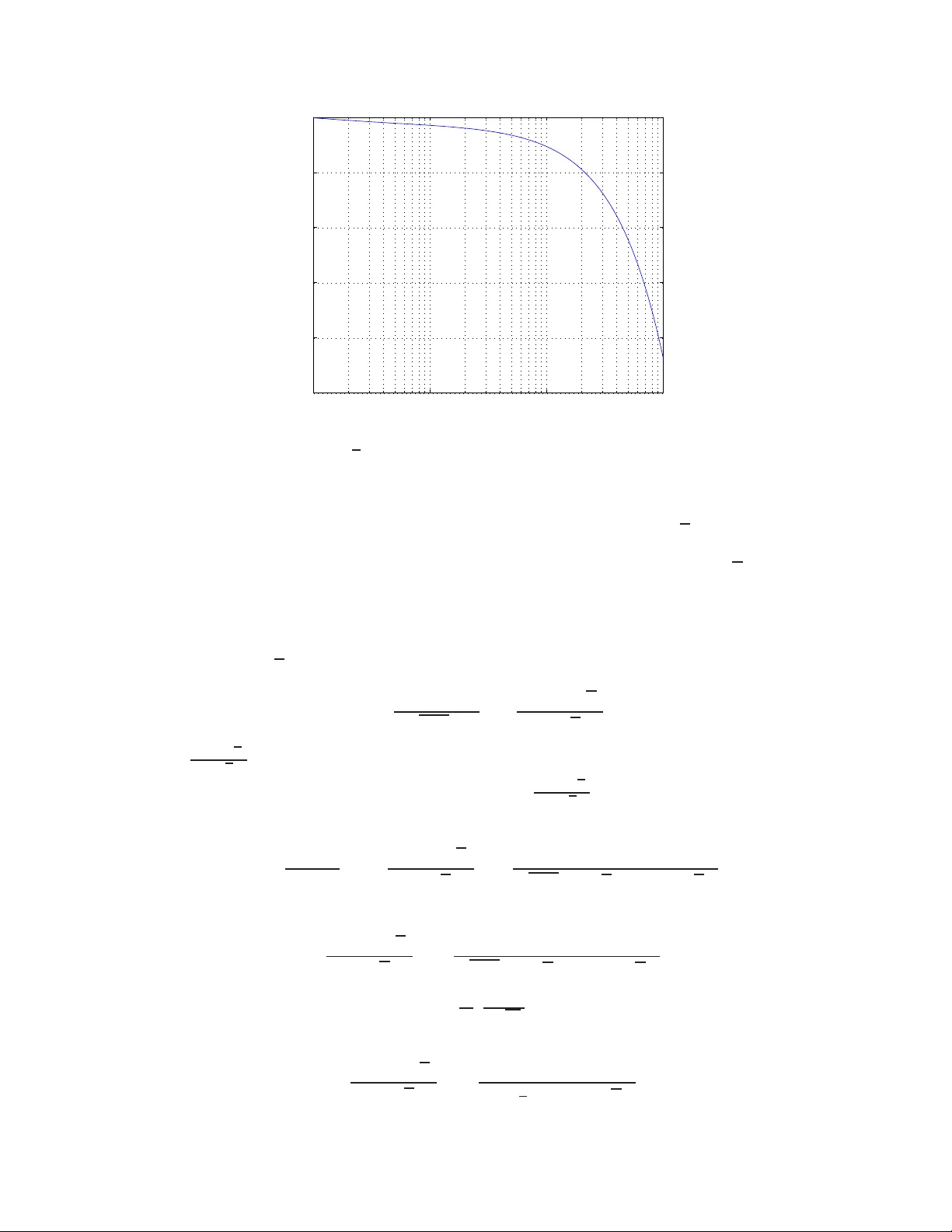

본 논문은 1~3비트 수준으로 낮춘 아날로그‑디지털 변환기(ADC)의 정밀도가 실현 가능한 통신 시스템에 미치는 영향을 정보이론적으로 분석한다. 실수값 AWGN 채널에 K‑레벨 양자화를 적용했을 때, 채널 용량은 최대 K+1개의 질점으로 구성된 이산 입력 분포로 달성될 수 있음을 증명하고, 1비트 양자화에서는 이진 반대극 신호가 모든 SNR에서 최적임을 보인다. 다비트 양자화에 대해서는 수치적으로 용량을 계산하고, 2~3비트 양자화가 20 dB…

저자: Jaspreet Singh, Onkar Dabeer, Upamanyu Madhow

본 논문은 현대 디지털 통신 수신기의 핵심인 디지털 신호 처리(DSP)와 고속·고대역폭 시스템에서 필수적인 아날로그‑디지털 변환기(ADC)의 정밀도 사이의 트레이드오프를 정보이론적인 관점에서 체계적으로 분석한다. 현재 상용 시스템에서는 8~12비트 수준의 ADC가 일반적이지만, 샘플링 속도가 급증함에 따라 이러한 고정밀 ADC는 전력 소모와 비용 면에서 비현실적이 된다. 따라서 저정밀(1~3비트) ADC를 채택했을 때 통신 성능이 어떻게 변하는지를 정량화하는 것이 본 연구의 핵심 목표이다.

연구는 실수값 연속시간 AWGN 채널에 K‑레벨 구간 양자화기(Q)를 적용한 메모리리스 이산시간 모델 Y = Q(X+N) 을 기반으로 한다. 여기서 X는 평균 전력 제약 E

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기