터보 코드 최소 지연 디코딩을 이용한 상위 계층 FEC

** 본 논문은 이진 소거 채널(BEC)에서 상위 계층 오류 정정(UL‑FEC)용으로 설계된 병렬 터보 코드의 최소 지연 디코딩 알고리즘을 제안한다. 수신된 심볼이 도착하는 즉시 트레시에서 전이들을 제거하며, 두 트레시 사이의 하드 비트 교환을 통해 전파한다. 알고리즘은 선형 시간 복잡도를 유지하면서 LDPC 코드와 비교해 5~10% 수준의 오버헤드로 거의 용량에 근접한 성능을 보인다. **

저자: Ghassan M. Kraidy, Valentin Savin

**

본 논문은 상위 계층 오류 정정(Upper‑Layer FEC, UL‑FEC) 상황을 목표로, 이진 소거 채널(Binary Erasure Channel, BEC)에서 병렬 터보 코드(parallel turbo code)의 최소 지연 디코딩 알고리즘을 제안한다. 전통적인 터보 코드 디코딩은 전체 코드워드가 수신된 뒤에야 시작되는 SISO(Soft‑Input Soft‑Output) 포워드‑백워드(FB) 혹은 Viterbi 알고리즘을 기반으로 한다. 이러한 방식은 지연이 크고, 특히 패킷 손실이 빈번한 네트워크 환경에서는 비효율적이다. 반면, BEC에서는 심볼이 ‘알려짐(0/1)’ 혹은 ‘소거(∅)’ 두 가지 상태만 존재하므로, 소프트 정보가 필요 없으며 하드 비트 교환만으로도 최적 복구가 가능하다는 점을 이용한다.

### 1. 시스템 모델

- 병렬 터보 코드는 두 개의 재귀적 시스템적 컨볼루션(RSC) 코드(예: (7,5)_8)와 인터리버 Π로 구성된다.

- 기본 코드율은 1/3이며, 필요에 따라 패턴을 펀칭(puncture)하여 1/2, 2/3 코드율을 만든다.

- 전송된 심볼은 정보 비트와 두 개의 패리티 비트(각 RSC 코드에서 생성)로 이루어지며, BEC에서 각 비트는 확정(0/1) 혹은 소거 상태가 된다.

### 2. 최소 지연 디코딩 알고리즘

알고리즘은 다음 단계로 구성된다.

1. **초기화**: 각 트레시 단계 i에 대해 전이 행렬 M₁(i), M₂(i)를 전부 가능한 전이(T_xx)로 초기화하고, 시작·종료 상태를 0 상태로 고정한다.

2. **수신**: 비트 r가 도착하면 해당 트레시의 전이 행렬에 논리 AND 연산을 적용한다. 정보 비트는 두 트레시 모두에 적용하고, 패리티 비트는 해당 트레시만 적용한다.

3. **전파(Propagation)**: M_d(t) 행렬에 전부 0인 행(또는 열)이 생기면, 인접 단계(t‑1 또는 t+1)의 행(또는 열)도 0으로 만든다. 이는 “상태가 차단되면 전이도 차단된다”는 논리를 구현한다.

4. **복제(Duplication)**: 한 트레시에서 비트가 확정되면 인터리버를 통해 다른 트레시에서도 동일 비트를 고정하고, 다시 전파 과정을 수행한다.

5. **새로운 수신**: 전파가 멈추면 다시 수신 단계로 돌아가 새 비트를 처리한다.

6. **디코딩 종료**: 모든 단계 i에 대해 M₁(i)⊆T_bx, M₂(i)⊆T_bx가 만족되면 디코딩 성공이며, 수신된 비트 수 r_stop을 기록한다.

알고리즘의 효율성을 나타내는 지표로 **비효율 계수 μ = r_stop / K**를 정의한다. μ=1이면 MDS 코드와 동일하게 K개의 심볼만으로 K개의 정보를 복구한다는 의미이다.

### 3. 복잡도 분석

- 전이 행렬은 2^{L‑1}×2^{L‑1} 크기로, L=3(4 상태)인 경우 4×4 행렬만 필요하다.

- 각 단계에서 수행되는 연산은 행렬 간 논리 AND와 행/열 검사이며, 이는 O(1) 시간에 수행된다.

- 전체 트레시 길이 K에 대해 O(K) 시간 복잡도를 가지며, 메모리 요구량도 O(K)이다.

- k와 L이 커지면 전이 행렬 크기가 2^{k+L‑1}이 되므로 지수적 증가가 있지만, 실제 설계에서는 k=1, L=3 정도가 충분히 강력한 성능을 제공한다.

### 4. 시뮬레이션 결과

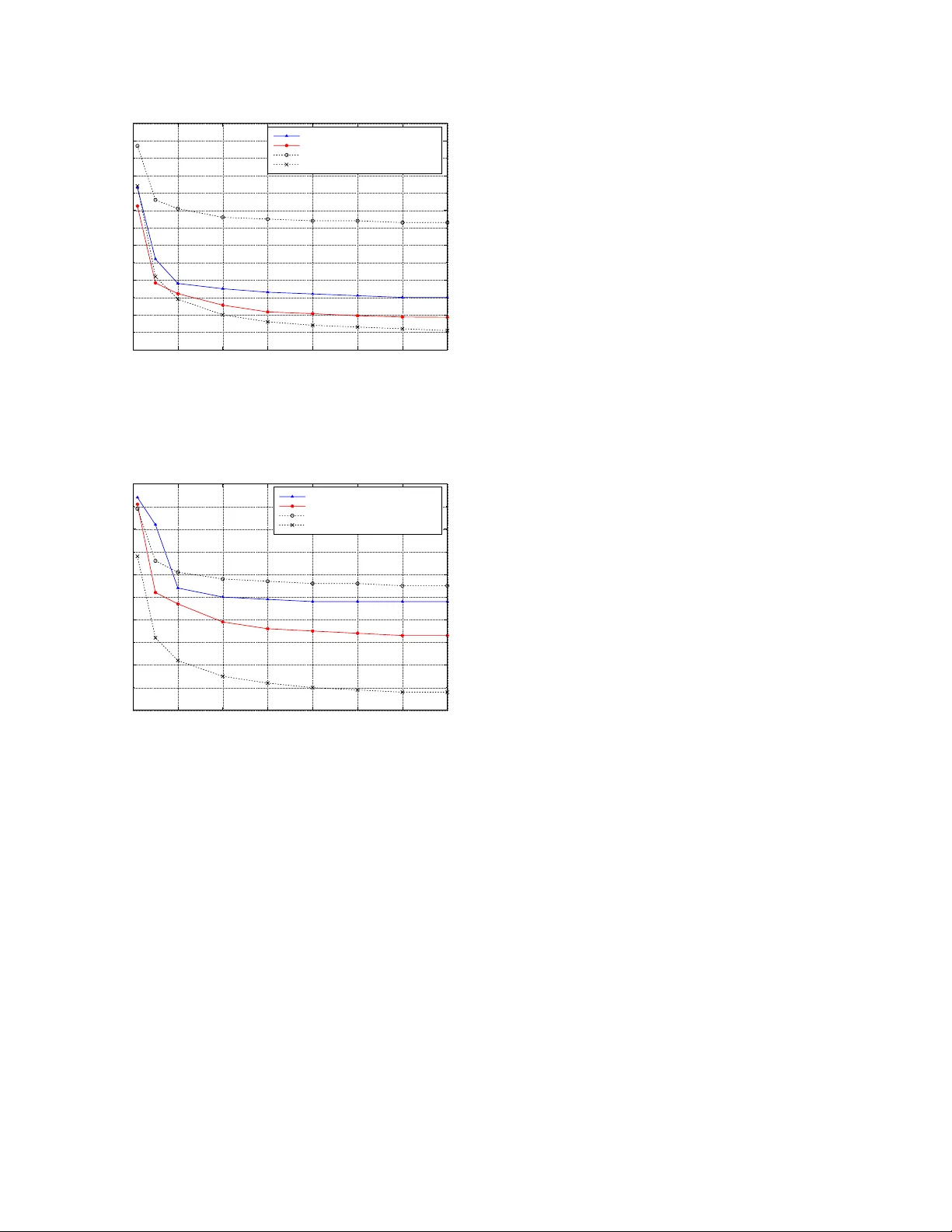

- **코드율**: R_c=1/3, 1/2, 2/3을 평가하였다.

- **인터리버**: 무작위 PR 인터리버와 최적화된 QC(Quasi‑Cyclic) 2‑차원 인터리버를 사용하였다. QC 인터리버는 최소 거리 d_min을 로그 규모로 증가시켜 성능을 향상시킨다.

- **비교 대상**: 규칙적(staircase) LDPC(4‑1)와 비정규(irregular) LDPC를 BEC에 최적화된 density evolution으로 설계하였다.

- **결과**:

- PR 인터리버를 사용한 RSC(7,5) 터보 코드는 μ_av≈1.09(9% 오버헤드)이며, QC 인터리버는 μ_av≈1.07(7% 오버헤드)로 LDPC와 거의 동등하거나 약간 우수했다.

- R_c=1/2, 2/3에서도 비슷한 수준의 μ_av를 보였으며, 특히 고율에서는 펀칭에 따른 오버헤드가 감소해 전체 효율이 향상되었다.

- LDPC 코드는 설계에 따라 μ_av가 1.04~1.12 정도였으며, 복잡도 측면에서 메시지‑패싱 반복 횟수에 비례해 연산량이 증가한다.

### 5. 논의 및 활용 가능성

- **지연 감소**: 수신 즉시 디코딩을 시작하므로, 전송 지연이 크게 감소한다. 이는 실시간 스트리밍, 위성 방송, 사물인터넷 등 재전송이 어려운 환경에 적합하다.

- **구현 용이성**: 전이 행렬을 미리 저장하고 논리 연산만 수행하므로, FPGA나 ASIC에 구현하기 쉽다.

- **확장성**: 현재는 BEC에 초점을 맞췄지만, erasure 외에 오류가 포함된 채널에서는 추가적인 소프트 정보가 필요할 수 있다. 하이브리드 방식(soft‑hard 결합)으로 확장 가능성이 있다.

- **제한점**: 높은 erasure 확률(p>0.7)에서는 전파가 멈추어 디코딩이 실패할 수 있다. 이 경우 상위 계층에서 재전송 혹은 추가적인 레이어 FEC와 결합해야 한다.

결론적으로, 본 논문은 BEC 환경에서 터보 코드를 이용한 UL‑FEC에 최적화된 최소 지연 디코딩 프레임워크를 제시하고, LDPC 기반 솔루션과 비교해 비슷하거나 더 낮은 오버헤드와 구현 단순성을 입증하였다. 이는 차세대 네트워크에서 지연 민감형 데이터 전송을 위한 실용적인 대안이 될 수 있다.

**

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기