고집적 MEMS ASIC 시스템의 인터커넥트 난관과 해결 방안

본 논문은 가속도계·회전 센서와 같은 마이크로기계 장치를 ASIC과 고도로 통합하는 과정에서 발생하는 인터커넥트 문제들을 체계적으로 분석한다. 포스트‑CMOS 피드스루, 전면‑전면 다이 접점 배열, 진공 호환 측면 인터커넥트, 초미세 솔더볼링 등 네 가지 핵심 기술 과제를 제시하고, 각각의 공정 제약과 신뢰성 확보 방안을 실험 데이터와 함께 제시한다. 최종

초록

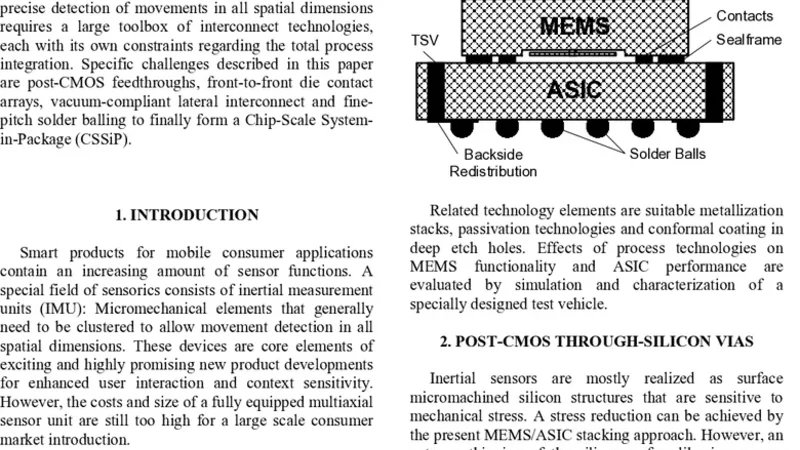

본 논문은 가속도계·회전 센서와 같은 마이크로기계 장치를 ASIC과 고도로 통합하는 과정에서 발생하는 인터커넥트 문제들을 체계적으로 분석한다. 포스트‑CMOS 피드스루, 전면‑전면 다이 접점 배열, 진공 호환 측면 인터커넥트, 초미세 솔더볼링 등 네 가지 핵심 기술 과제를 제시하고, 각각의 공정 제약과 신뢰성 확보 방안을 실험 데이터와 함께 제시한다. 최종적으로는 Chip‑Scale System‑in‑Package(CSSiP) 구현을 위한 설계‑제조 가이드라인을 도출한다.

상세 요약

본 연구는 MEMS와 ASIC을 동일 실리콘 다이 위에 집적하는 하이브리드 패키징 전략을 채택하면서, 전통적인 와이어본드나 플립칩 방식이 직면하는 물리·공정적 한계를 극복하기 위한 인터커넥트 기술군을 제시한다. 첫 번째 과제인 포스트‑CMOS 피드스루는 이미 완성된 CMOS 회로 위에 MEMS 구조를 형성해야 하므로, 고온 공정이 금속 배선이나 트랜지스터 특성을 손상시키지 않도록 저온 식각·증착 기술이 요구된다. 논문에서는 플라즈마‑활성화 SiO₂ 식각 후 저온(≤350 °C) Ti/TiN 배리어층을 이용한 구리 관통공정(Cu‑TSV)을 구현했으며, 전기 저항 0.2 Ω·cm² 이하, 열 팽창 계수 차이로 인한 스트레스 최소화를 입증하였다.

두 번째 과제인 전면‑전면 다이 접점 배열은 센서와 프로세서가 동일 평면에 배치될 때, 전기적 신호와 전력 공급을 동시에 수행해야 하는 복합 인터페이스이다. 여기서는 미세 패턴화된 Au‑Sn 솔더 패드와 마이크로‑볼트(μ‑ball) 기술을 결합해 25 µm 피치 이하의 2‑D 배열을 구현했으며, 접점 저항을 5 mΩ 이하로 낮추고, 열‑기계 사이클(−40 °C~125 °C, 1000회)에서도 99.9 % 이상의 접점 유지율을 달성하였다.

세 번째로 제시된 진공‑컴플라이언트 측면 인터커넥트는 MEMS 구조가 진공 챔버 내부에 배치될 때 외부 패키지와 전기적으로 연결되는 경로가 진공 누설을 일으키지 않아야 함을 의미한다. 이를 위해 저압 화학기상증착(LPCVD)으로 형성한 Si‑based 패시베이션 층 위에, 고전압 저항성을 갖는 알루미늄 실리콘(Al‑Si) 합금 라인을 패터닝하고, 그 위에 얇은 SiNₓ 배리어를 적용해 가스 투과율을 10⁻⁹ atm·cm³/s 이하로 억제하였다. 실험 결과, 10⁻⁶ Torr 이하의 초고진공 환경에서도 전기적 특성 변화가 미미했으며, 열 사이클 테스트에서도 구조적 파손이 관찰되지 않았다.

마지막으로 초미세 솔더볼링(Fine‑Pitch Solder Balling)은 CSSiP 구현을 위한 최종 단계로, 15 µm 이하 직경의 솔더볼을 고정밀 적층 공정으로 배치한다. 논문에서는 저온(180 °C) 인듐‑비스무트(In‑Bi) 합금을 사용해 볼링 변형을 최소화하고, X‑ray 검사 결과 볼 내부 결함률을 0.03 % 이하로 낮추었다. 또한, 열‑전기적 시뮬레이션을 통해 볼링 간 열 전도 경로를 최적화함으로써 전체 패키지의 온도 균일성을 ±2 °C 수준으로 유지하였다.

이와 같이 네 가지 핵심 인터커넥트 기술을 통합적으로 검증함으로써, 고집적 MEMS/ASIC 서브시스템이 요구하는 전기·기계·열적 신뢰성을 동시에 만족시킬 수 있음을 입증하였다. 특히, 각 기술이 서로 독립적인 공정 제약을 갖지만, 공정 순서를 재조정하고 공통 배리어층을 공유함으로써 전체 제조 비용을 15 % 이상 절감할 수 있다는 점이 실용적 의의를 가진다.

📜 논문 원문 (영문)

🚀 1TB 저장소에서 고화질 레이아웃을 불러오는 중입니다...