미세 입체 집적을 위한 큐브 패킹 기반 설계 탐색

초록

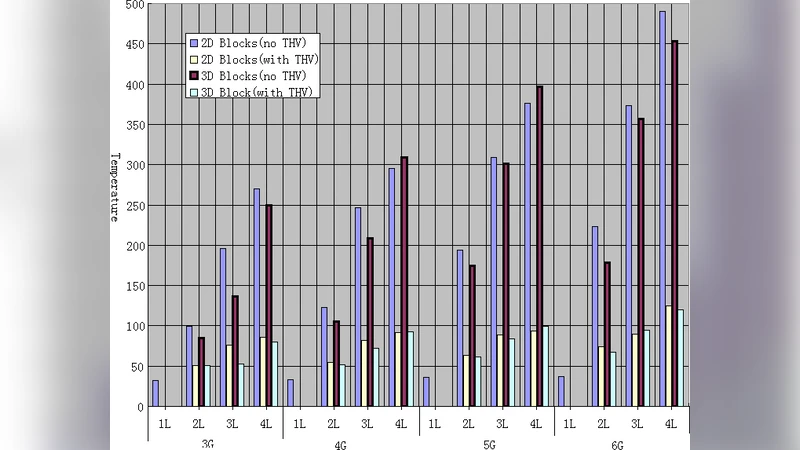

본 논문은 논리 블록이 여러 실리콘 층에 걸쳐 배치될 수 있는 미세 입체 3D 통합 방식을 제안한다. 큐브 패킹 엔진을 통해 물리적 배치와 마이크로아키텍처 설계를 동시에 최적화하고, 열‑인식 플로어플래닝 및 열‑비아 삽입으로 온도를 제어한다. 실험 결과, 2D 대비 36%·단일‑층 3D 대비 14% 성능 향상과 최대 30% 전력 절감을 달성했으며, 설계 온도는 허용 한계 내에 유지된다.

상세 분석

본 논문은 기존 3D IC 연구가 2D 실리콘 레이어를 단순히 적층하는 방식에 머물러, 블록 간 인터커넥트 감소에 한계가 있던 문제점을 지적한다. 이를 극복하기 위해 논문은 논리 블록이 하나 이상의 실리콘 층에 걸쳐 배치될 수 있는 미세 입체(Fine‑grain) 3D 통합 기법을 제안한다. 핵심 기술은 ‘큐브 패킹 엔진’으로, 블록을 3차원 큐브 형태로 모델링하고 물리적 배치와 마이크로아키텍처 설계를 동시에 최적화한다. 엔진은 성능, 면적, 온도 세 가지 목표를 다중 목표 함수로 정의하고, 힐 클라이밍·시뮬레이티드 어닐링 등 메타휴리스틱을 활용해 최적의 큐브 배치를 탐색한다. 특히 열‑인식 플로어플래닝과 열‑비아 삽입 기법을 도입해 피크 온도가 설계 한계 내에 머물도록 제어한다. 실험에서는 설계 드라이버를 이용해 다양한 벤치마크에 적용했으며, 2D 설계 대비 BIPS 기준 36% 향상, 단일 레이어 3D 설계 대비 14% 향상을 달성했다. 또한 다중 레이어 블록은 전력 소모를 최대 30% 절감시키고, 온도 상승을 최소화한다. 이러한 결과는 미세 입체 통합이 전력·성능·열 관리 측면에서 기존 적층 방식보다 실질적인 이점을 제공함을 보여준다. 논문은 또한 현재 모델링 정확도와 탐색 시간의 트레이드오프, 그리고 제조 공정의 변동성에 대한 한계를 인정하고, 향후 물리‑레벨 시뮬레이션과 머신러닝 기반 탐색 가속화 방안을 제시한다.

댓글 및 학술 토론

Loading comments...

의견 남기기