디자인 공간 탐색으로 인터리버 최적화

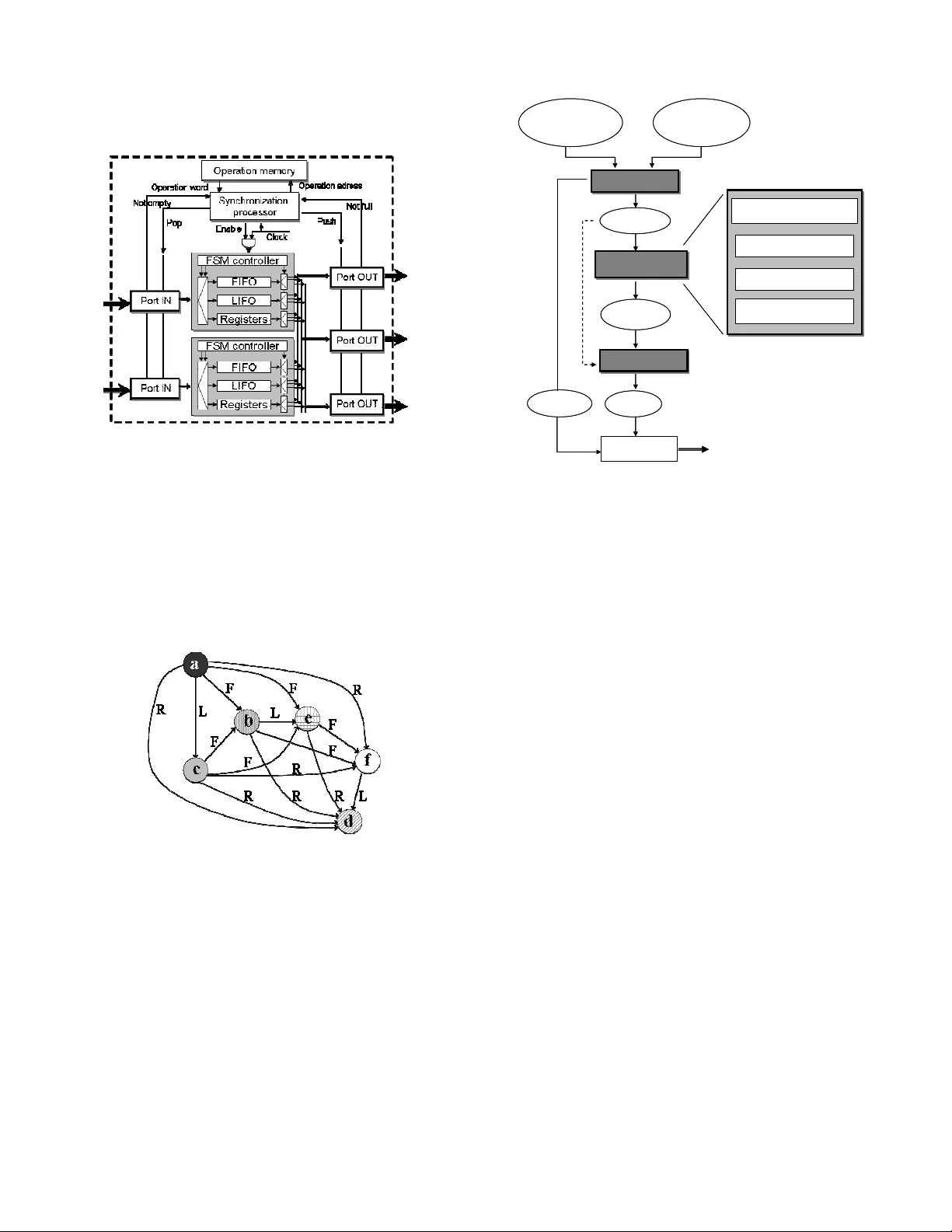

본 논문은 통신 어댑터 설계에 필요한 디자인 공간 탐색을 그래프 기반 모델인 Resource Constraints Graph(RCG)로 형식화하고, 자동으로 최적화된 Space‑Time Adapter(STAR)를 생성하는 흐름을 제시한다. C 수준의 인터리버 스케줄링과 성능 요구사항을 입력으로 받아, 저장소 바인딩·크기 결정·아키텍처 최적화를 수행하며, Ultra‑Wideband 인터리버 사례를 통해 설계 탐색 효율성을 검증한다.

저자: Cyrille Chavet (LESTER, STM), Philippe Coussy (LESTER)

본 논문은 디지털 신호 처리와 통신 시스템에서 데이터 교환을 담당하는 어댑터, 특히 인터리버 설계에 초점을 맞추어, 설계 공간 탐색을 효율적으로 수행할 수 있는 방법론을 제시한다. 서론에서는 현대 통신 표준이 요구하는 고대역폭·저지연·높은 BER 성능을 달성하기 위해 터보‑코드와 같은 복합 코덱이 병렬화되어 구현되는 현황을 설명한다. 이러한 병렬 구조에서는 여러 프로세싱 엔티티가 동일 메모리(RAM)에 동시에 접근하면서 “collision” 문제가 발생하고, 이는 전체 시스템 지연을 크게 늘린다. 기존 연구들은 충돌을 회피하기 위해 전용 충돌‑프리 인터리버 설계, 버퍼링 네트워크, 소프트웨어/재구성 가능한 구현 등을 제안했지만, 각각 표준 호환성, 면적·전력 효율성, 설계 복잡도 등의 한계를 가지고 있다.

이에 저자들은 이전 연구

원본 논문

고화질 논문을 불러오는 중입니다...

댓글 및 학술 토론

Loading comments...

의견 남기기