맞춤형 3D 적층 DRAM 설계를 위한 DreamRAM 모델링 툴

📝 원문 정보

- Title: 맞춤형 3D 적층 DRAM 설계를 위한 DreamRAM 모델링 툴

- ArXiv ID: 2512.12106

- 발행일:

- 저자: Unknown

📝 초록 (Abstract)

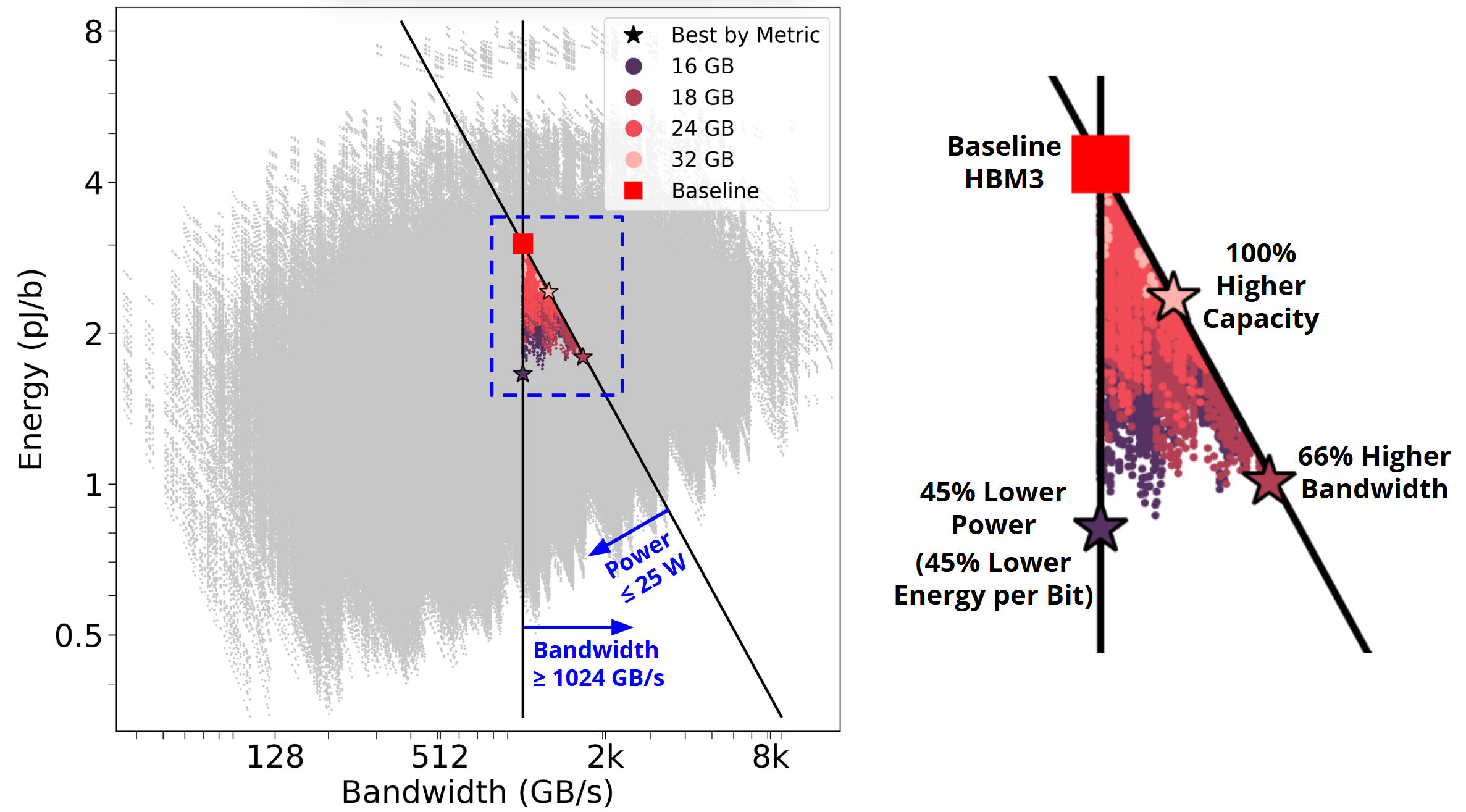

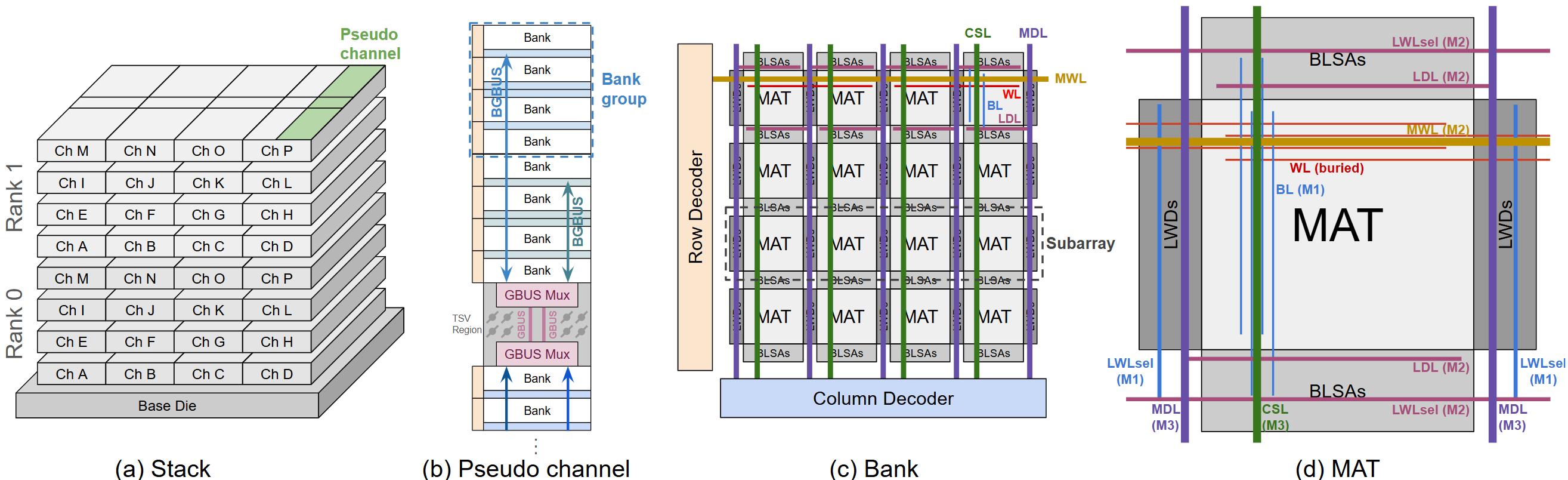

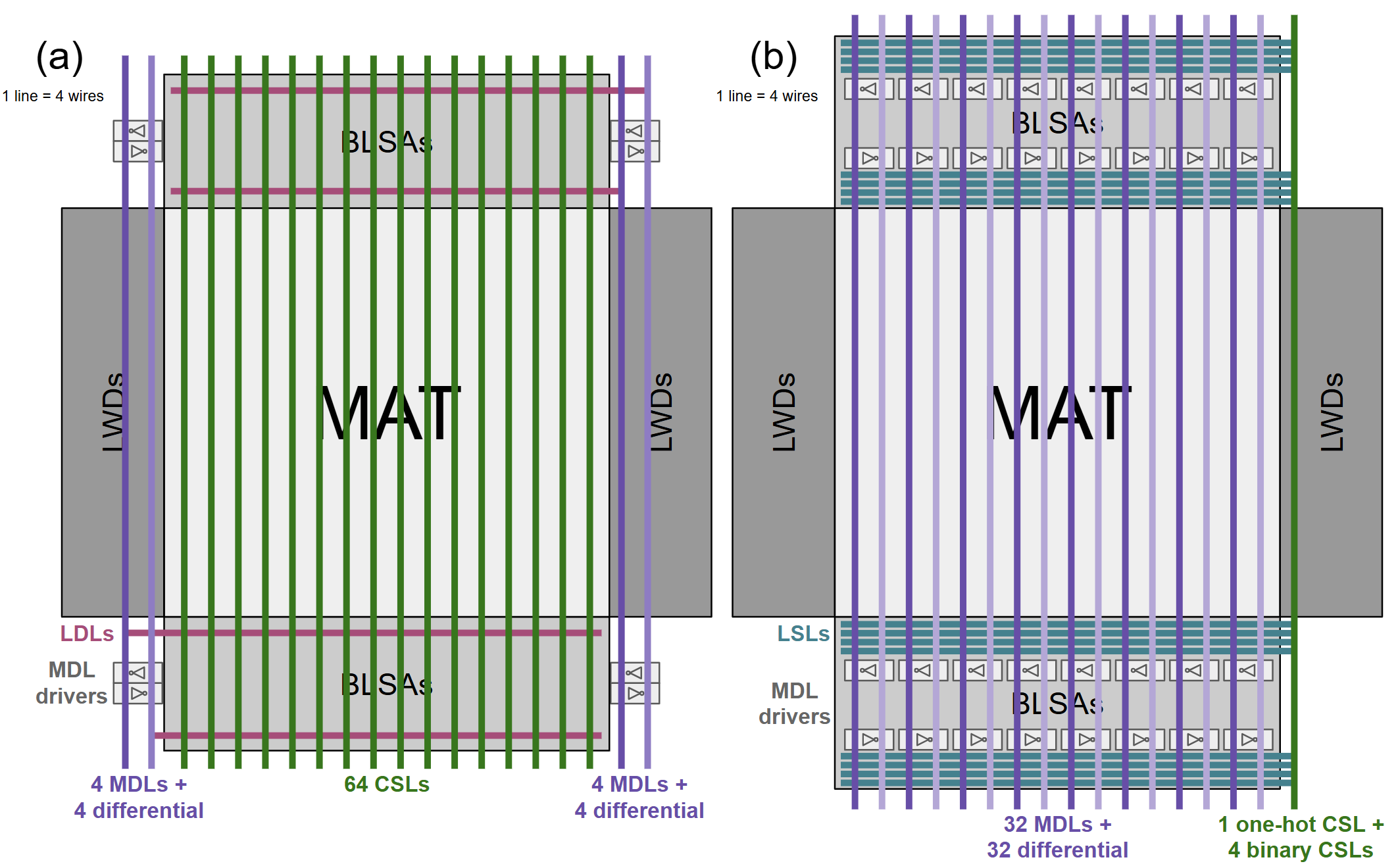

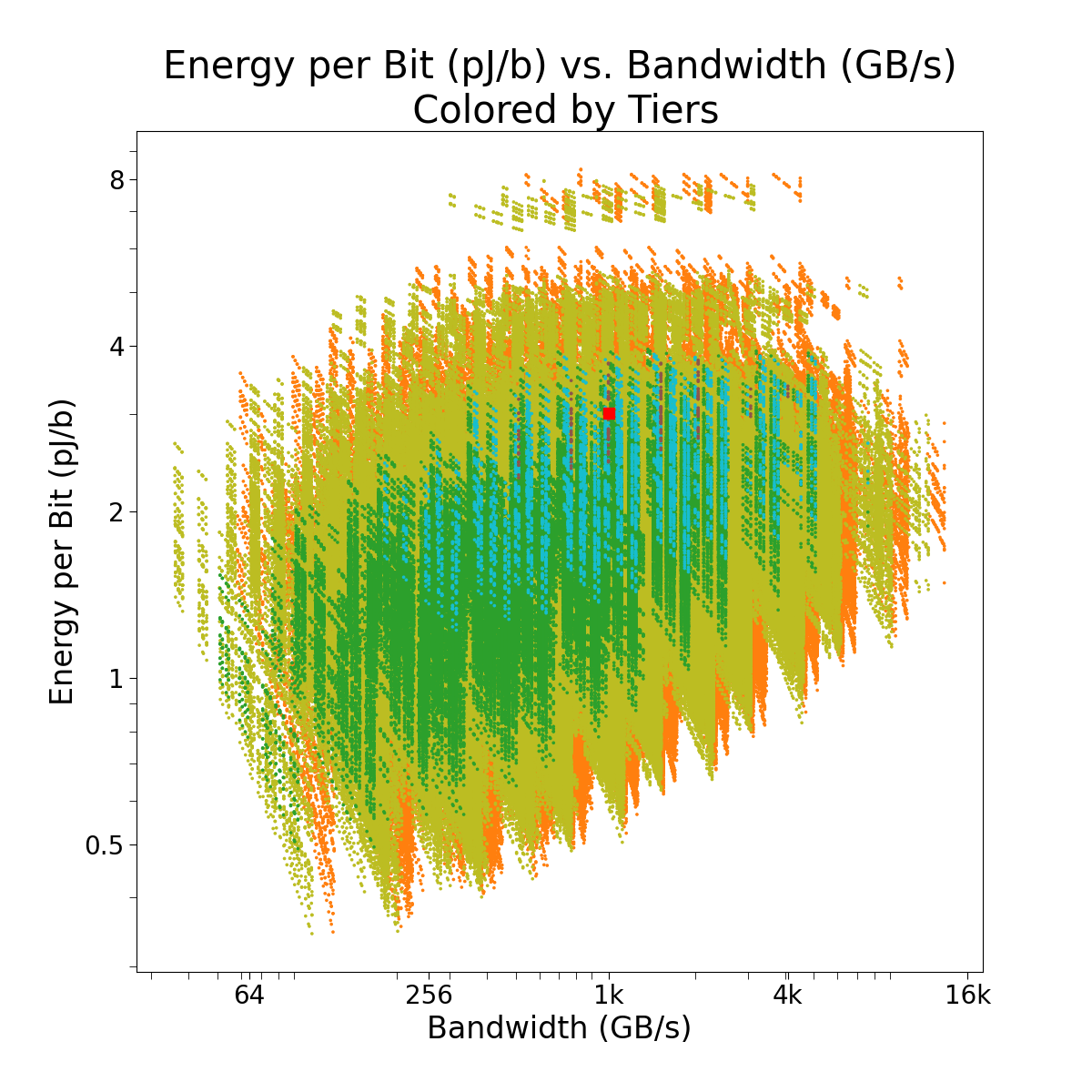

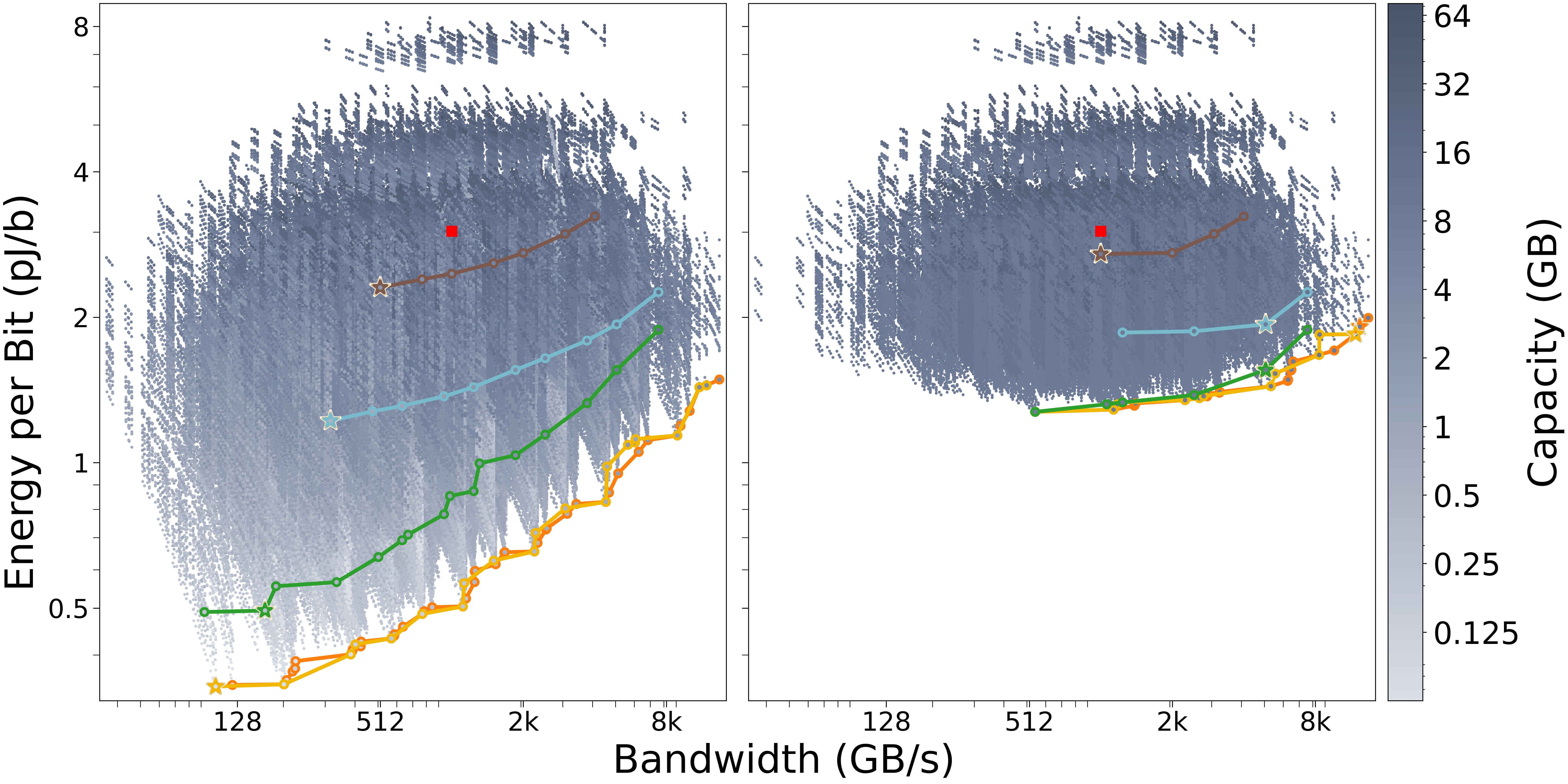

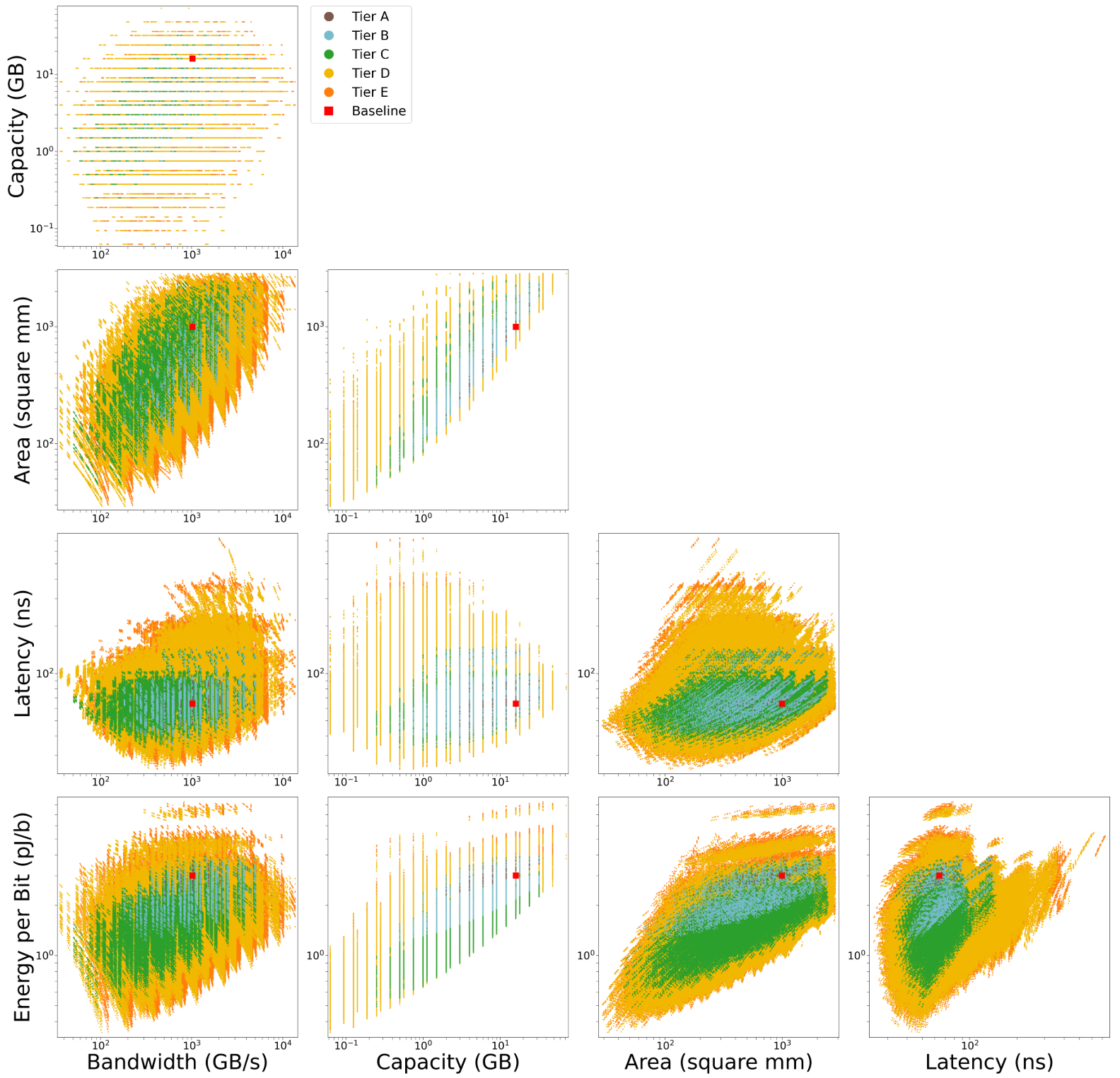

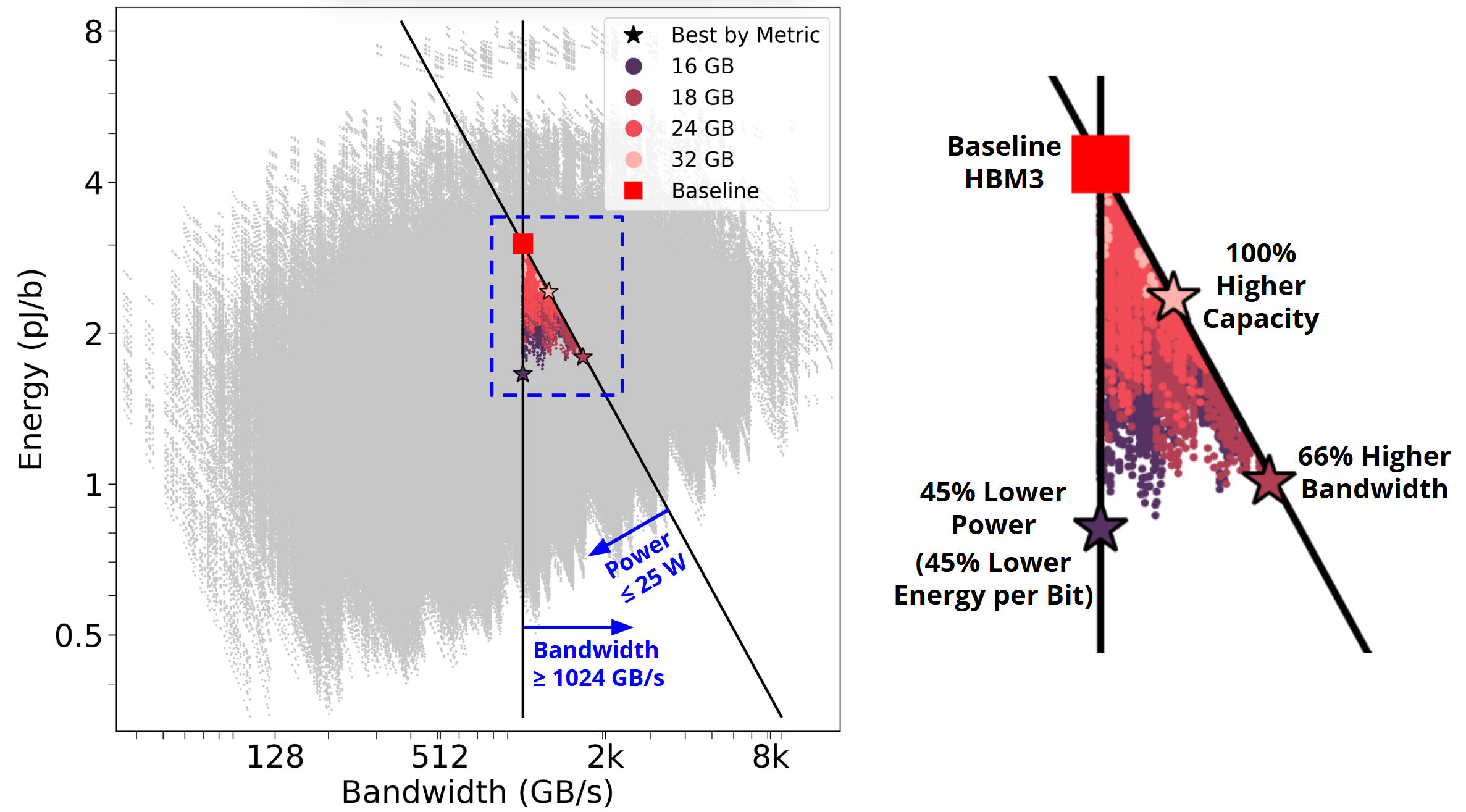

3D 적층 DRAM은 고성능 컴퓨팅, 그래픽, 머신러닝 등 고대역폭·고밀도 요구가 있는 분야에서 핵심 기술로 부상하고 있다. 그러나 다양한 애플리케이션은 전력·성능·면적에 대해 서로 다른 요구를 가지고 있어 고정된 범용 DRAM 설계만으로는 모두 만족시키기 어렵다. 적층 구조는 3D 통합과 전체 다이 면적 확대를 통해 DRAM 설계 공간을 크게 확장한다. 이러한 애플리케이션 특화 메모리 아키텍처 설계 공간을 열고 탐색하기 위해, 우리는 DreamRAM이라는 구성 가능한 대역폭, 용량, 에너지, 지연, 면적 모델링 툴을 제시한다. DreamRAM은 MAT, 서브어레이, 뱅크, 뱅크 간 인터커넥트 수준에서 세밀한 설계 파라미터를 노출하고, 기존 연구의 부분 페이지 및 서브어레이 병렬성 기법을 확장하여 이전에 탐색되지 않았던 설계 공간을 개방한다. 또한 와이어 피치·폭·길이·정전용량·스케일링 파라미터를 분석적으로 모델링하여 물리적 레이아웃 및 라우팅 선택에 따른 성능 트레이드오프를 포착한다. 라우팅 인식을 통해 DreamRAM은 맞춤형 MAT‑레벨 라우팅 스킴인 Dataline‑Over‑MAT(DLOMAT)를 모델링하여 대역폭 트레이드오프를 개선한다. DreamRAM은 공개된 산업용 HBM3·HBM2E 설계와 비교해 캘리브레이션 및 검증을 수행하였다. 풍부한 설계 공간 내에서 우리는 기준 설계 대비 각각 66 % 높은 대역폭, 100 % 높은 용량, 45 % 낮은 전력·에너지(비트당)를 달성하는 설계를 동일 대역폭·동일 용량·동일 전력 조건에서 찾아냈다.💡 논문 핵심 해설 (Deep Analysis)

분석 방법론 측면에서 DreamRAM은 와이어 피치, 폭, 길이, 정전용량, 스케일링 파라미터 등을 수식화하여 물리‑전기적 특성을 정량화한다. 이는 실리콘 레벨의 설계 변화를 빠르게 시뮬레이션 없이도 평가할 수 있게 해, 설계 탐색 공간을 수천 개에서 수만 개 수준으로 확장한다. 논문은 또한 HBM3·HBM2E와의 캘리브레이션을 통해 모델 정확성을 검증했으며, 오차 범위가 수% 이내임을 보고함으로써 실무 적용 가능성을 높였다.

실험 결과는 ‘동일 대역폭(iso‑bandwidth)’, ‘동일 용량(iso‑capacity)’, ‘동일 전력(iso‑power)’ 조건에서 각각 66 % 대역폭 향상, 100 % 용량 확대, 45 % 전력·에너지 절감을 달성한 설계를 제시한다. 이는 단순히 하나의 메트릭을 최적화하는 것이 아니라, 다중 목표를 동시에 만족시키는 설계가 가능함을 증명한다. 다만, 논문은 물리적 레이아웃 제약 외에 제조 공정 변동성, 열 관리, 신뢰성(예: TSV 스트레스) 등 실제 생산 단계에서 발생할 수 있는 이슈를 다루지 않았다. 향후 연구에서는 이러한 비이상적 요인을 모델에 통합하고, 머신러닝 기반 설계 탐색을 결합해 설계 효율성을 더욱 높이는 방안을 모색할 필요가 있다.

📄 논문 본문 발췌 (Translation)

📸 추가 이미지 갤러리