DWN FPGA 가속기에서 온도계 인코딩 구현 및 분석

📝 원문 정보

- Title: Implementation and Analysis of Thermometer Encoding in DWN FPGA Accelerators

- ArXiv ID: 2512.15251

- 발행일: 2025-12-17

- 저자: Michael Mecik, Martin Kumm

📝 초록 (Abstract)

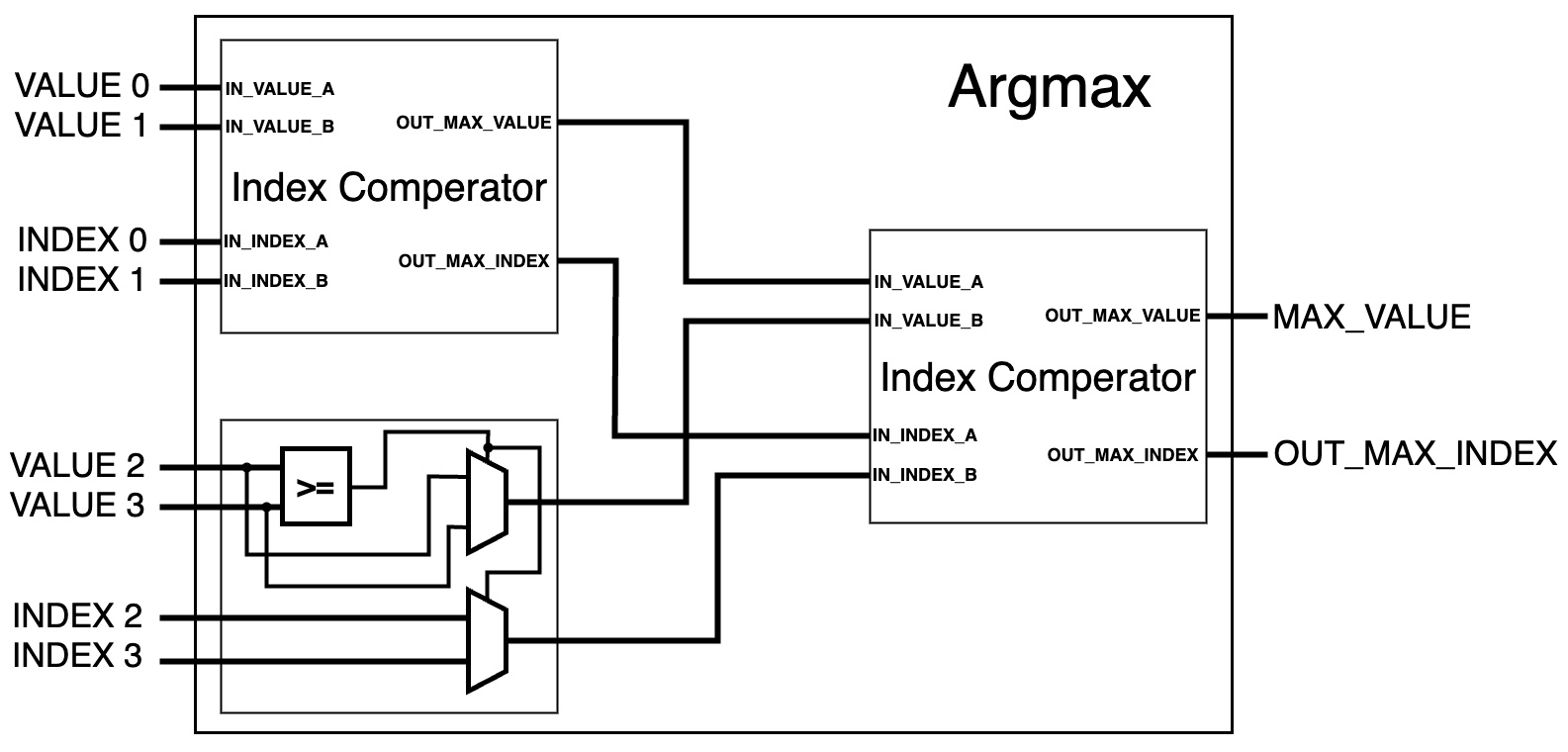

완전 병렬 신경망 가속기는 지연에 민감한 응용에서 높은 처리량을 제공하지만, FPGA의 제한된 하드웨어 자원으로 인해 설계에 제약을 받는다. 가중치 없는 신경망(WNN)은 산술 연산을 논리 기반 추론으로 대체함으로써 효율성을 높인다. 차별화된 가중치 없는 신경망(DWN)은 그래디언트 기반 학습을 통해 인코더와 LUT(Look‑Up Table) 층 사이의 연결을 최적화하여 자원 사용을 더욱 감소시킨다. 그러나 DWN은 온도계 인코딩에 의존하는데, 이 인코딩이 하드웨어 비용에 미치는 영향은 아직 충분히 평가되지 않았다. 본 논문은 온도계 인코딩을 명시적으로 포함한 DWN 하드웨어 생성기를 제시한다. Jet Substructure Classification(JSC) 작업에 대한 실험 결과, 인코딩이 LUT 사용량을 최대 3.20배까지 증가시켜 소규모 네트워크에서는 비용을 지배하게 됨을 확인하였다. 이는 DWN 가속기 설계 시 인코딩 비용을 고려한 최적화가 필요함을 강조한다.💡 논문 핵심 해설 (Deep Analysis)

논문은 이러한 인코딩 비용을 정량적으로 평가하기 위해 두 가지 핵심 요소를 도입한다. 첫째, 온도계 인코더를 포함한 하드웨어 생성기를 설계해 자동으로 RTL 코드를 생성하고, 인코딩 전·후의 자원 사용량을 비교한다. 둘째, 실제 물리적 작업인 Jet Substructure Classification(JSC) 데이터셋을 사용해 네트워크 규모(층 수·노드 수)별 LUT 사용량 변화를 측정한다. 실험 결과는 특히 파라미터 수가 적은 소규모 DWN에서 인코딩이 전체 LU…