범용 연결성을 갖춘 FPGA 기반 뉴로모픽 프로세서

읽는 시간: 2 분

...

📝 원문 정보

- Title: Neuromorphic Processor Employing FPGA Technology with Universal Interconnections

- ArXiv ID: 2512.10180

- 발행일: 2025-12-11

- 저자: Pracheta Harlikar, Abdel-Hameed A. Badawy, Prasanna Date

📝 초록 (Abstract)

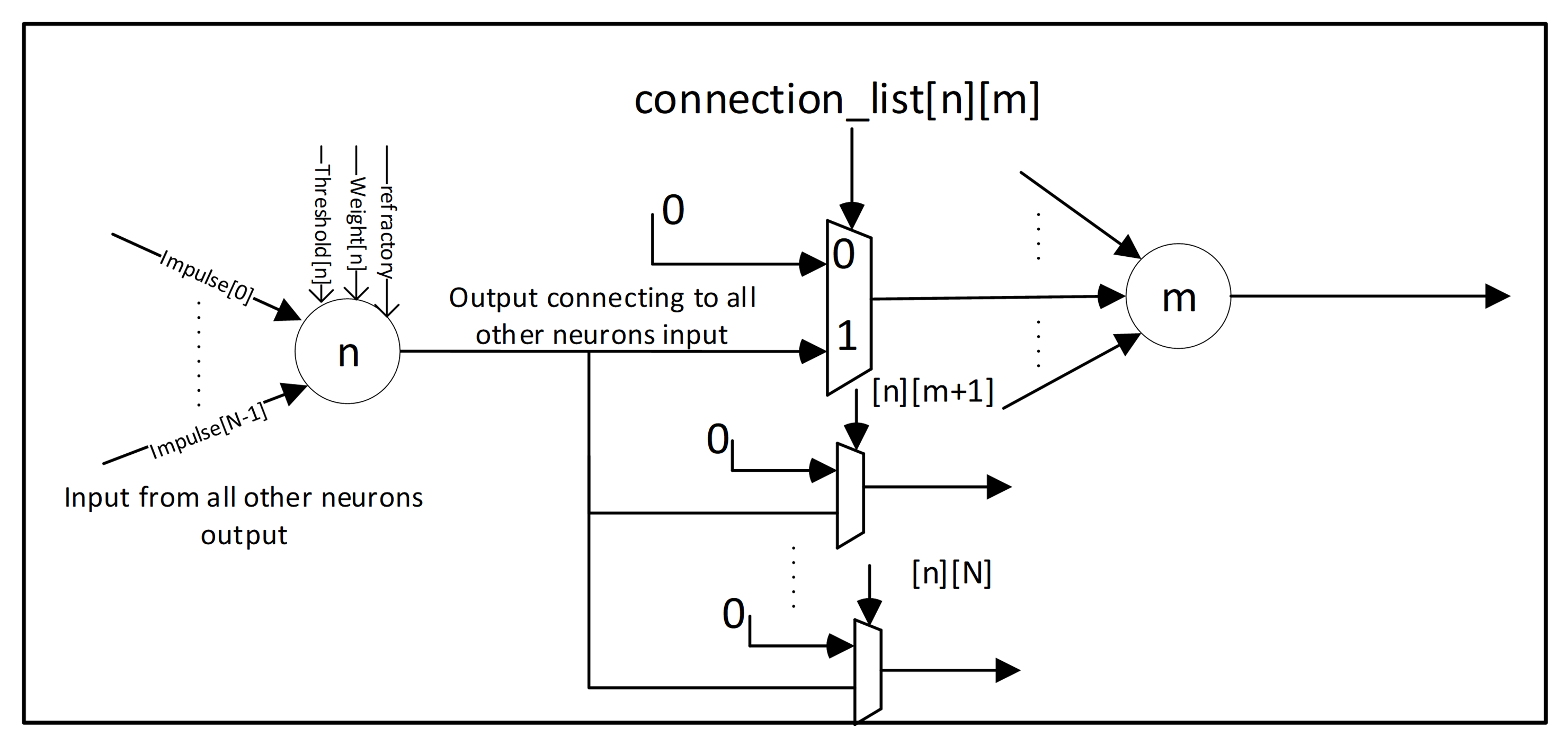

뉴로모픽 컴퓨팅은 생물학적 신경 시스템에서 영감을 받아 초저전력 및 실시간 추론 응용에 큰 가능성을 제시한다. 그러나 유연하고 오픈소스인 플랫폼에 대한 접근성이 제한되어 있어 널리 채택되고 실험하기가 어렵다. 본 논문에서는 저비용 Xilinx Zynq‑7000 FPGA 보드를 이용한 뉴로모픽 프로세서를 제안한다. 이 프로세서는 전-전 연결이 가능한 구성 가능한 인터커넥트를 제공하며, 임계값, 시냅스 가중치, 불응기 기간 등을 사용자 정의할 수 있는 누설 적분‑발화(LIF) 뉴런 모델을 구현한다. 호스트와의 통신은 UART 인터페이스를 통해 이루어져 하드웨어 재합성 없이 런타임 재구성이 가능하다. 제안된 아키텍처는 Iris 데이터셋 분류와 MNIST 손글씨 인식이라는 벤치마크를 이용해 검증하였다. 합성 후 결과는 설계가 에너지 효율적이며 확장 가능함을 보여주며, 실제 스파이킹 신경망 응용에 적합한 연구용 뉴로모픽 플랫폼으로서의 타당성을 입증한다. 프로젝트 완료 후 본 구현은 오픈소스로 공개될 예정이다.💡 논문 핵심 해설 (Deep Analysis)

구현 측면에서 가장 눈에 띄는 점은 UART 기반 호스트 인터페이스를 통해 파라미터를 실시간으로 업데이트 할 수 있다는 점이다. 이는 FPGA 재합성 없이도 가중치, 임계값, 불응기 등을 동적으로 조정할 수 있음을 의미한다. 다만 UART는 전송 속도가 제한적이므로 대규모 네트워크(수천~수만 뉴런)에서는 파라미터 전송에 병목이 발생할 가능성이 있다. 향후 USB‑3.0, Ethernet, 혹은 PCIe와 같은 …