저비용 FPGA용 WASM 서브셋 듀얼스택 마이크로프로세서 설계

📝 원문 정보

- Title: A WASM-Subset Stack Architecture for Low-cost FPGAs using Open-Source EDA Flows

- ArXiv ID: 2512.00974

- 발행일: 2025-11-30

- 저자: Aradhya Chakrabarti

📝 초록 (Abstract)

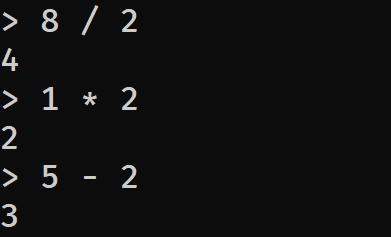

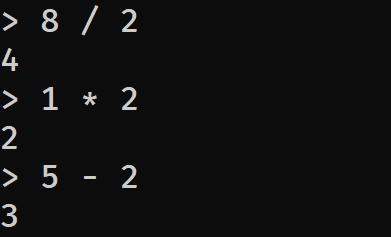

자원 제한이 있는 FPGA에서 소프트코어 프로세서는 코드 밀도가 낮고 폐쇄형 툴체인에 의존하는 경우가 많다. 본 논문은 32‑비트 듀얼‑스택 마이크로프로세서 아키텍처를 제안한다. ISA는 WebAssembly(WASM) 사양의 서브셋을 차용해 높은 코드 밀도를 달성했으며, Gowin GW1NR‑9(Tang Nano 9K) FPGA에 오픈‑소스 EDA 흐름으로 합성·배치하였다. 데이터와 리턴 스택을 별도로 두고, SPI Flash에서 직접 실행(XIP)함으로써 블록 RAM 사용을 최소화한다. 8‑엔트리 분산 RAM 스택은 논리 자원(≈80 %)과 라우팅 혼잡 사이의 균형을 제공한다. 단일 사이클 스택 연산에서 발생한 타이밍 해저드를 FSM 재설계로 해결했으며, 최종적으로 플래시 지연에 의해 제한된 27 MHz 안정 동작을 얻었다. 단일·다자리수 중위 계산기 등 간단한 애플리케이션을 성공적으로 구동한다.💡 논문 핵심 해설 (Deep Analysis)

둘째, 오픈‑소스 EDA 흐름을 전면에 내세운 점은 설계 투명성과 포터블성을 크게 높인다. Gowin FPGA는 전통적으로 자체 툴체인에 의존해 왔으며, IP 코어도 폐쇄형인 경우가 많다. 본 논문은 Yosys‑nextpnr‑open‑fpga‑loader 스택을 이용해 합성·배치를 수행함으로써, 설계자가 툴체인 내부 동작을 검증하고 필요에 따라 커스터마이징할 수 있는 기반을 제공한다. 이는 학계·산업 모두에서 재현 가능성을 보장하고, 장기적인 유지보수 비용을 절감한다는 장점을 가진다.

셋째, 듀얼‑스택 구조와 스택 깊이 파라미터화에 대한 실험적 분석이 돋보인다. 데이터 스택과 리턴 스택을 물리적으로 분리함으로써 스택 오버플로우와 언더플로우 검증을 단순화하고, 파이프라인 설계 시 데이터 의존성을 명확히 할 수 있다. 논문에서는 8‑엔트리 분산 RAM을 선택했으며, 이는 전체 LUT 사용량의 약 80 %를 차지하면서도 라우팅 혼잡을 최소화한다는 결과를 제시한다. 여기서 ‘80 %’라는 수치는 실제 구현에서 논리 자원의 대부분을 차지하지만, 여전히 타이밍 마진을 확보할 수 있음을 의미한다. 또한, 단일 사이클 스택 연산에서 발생한 타이밍 해저드를 FSM을 두 단계로 분리해 해결한 과정은 설계자의 실용적인 노하우를 제공한다.

성능 측면에서 27 MHz의 안정 동작은 플래시 액세스 지연이 병목임을 명시하고 있다. 이는 XIP 방식이 플래시 대기시간에 크게 의존한다는 점을 재확인한다. 향후 고속 SPI‑Flash 혹은 QSPI 인터페이스를 도입하면 클럭 주파수를 50 ~ 60 MHz 수준으로 끌어올릴 여지가 있다.

한계점으로는 현재 ISA가 WASM 전체 스펙의 일부분에 불과해, 복잡한 제어 흐름이나 SIMD 연산을 지원하지 못한다는 점이다. 또한, 9K급 FPGA의 제한된 BRAM을 전혀 활용하지 않음으로써, 대규모 데이터 버퍼링이 필요한 애플리케이션에는 부적합할 수 있다. 향후 연구에서는 WASM의 메모리 모델을 부분적으로 도입해 로컬 메모리 영역을 제공하거나, 파이프라인 깊이를 늘려 명령어 처리량을 향상시키는 방안을 모색할 필요가 있다. 전반적으로 이 논문은 저비용 FPGA 환경에서 오픈‑소스 기반 고밀도 코드를 구현할 수 있는 실용적인 로드맵을 제시하며, 교육용 및 임베디드 프로토타이핑 분야에 큰 파급 효과를 기대한다.

📄 논문 본문 발췌 (Translation)

📸 추가 이미지 갤러리