신경 부분 합과 스파이크 네트워크-온-칩을 갖춘 저전력 재구성형 뉴로모픽 가속기

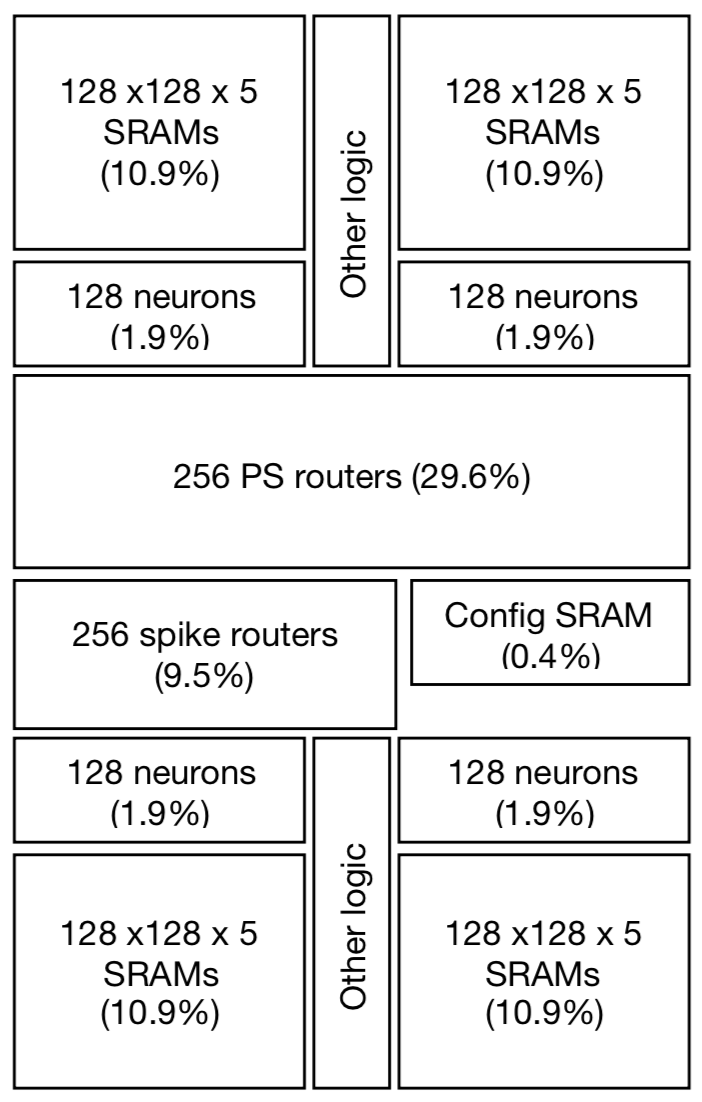

다음 세대의 장치 내 AI는 에너지 효율적인 딥 뉴럴 네트워크를 필요로할 것으로 보입니다. 뇌에서 영감을 받은 스퍼킹 뉴럴 네트워크(SNN)가 유망한 후보로 식별되었습니다. 곱셈이 필요하지 않게 함으로써 에너지 소모를 크게 줄일 수 있습니다. 장치 내 응용 프로그램의 경우 계산뿐만 아니라 통신도 상당량의 에너지와 시간을 차지합니다. 본 논문에서는 Shenjing이라는 재구성 가능한 SNN 아키텍처를 제안하며, 이는 모든 온칩 통신을 소프트웨어에 완전히 노출시켜 높은 정확도로 낮은 전력에서 SNN 모델 매핑이 가능하게 합니다. Shenjing과 달리 TrueNorth와 같은 이전의 SNN 아키텍처는 매핑을 위해 모델 수정 및 재학습이 필요합니다. 본 논문에서는 기존 인공신경망(ANN)인 다층 퍼셉트론, 컨볼루션 뉴럴 네트워크, 그리고 최신의 잔차 신경망까지 Shenjing에 성공적으로 매핑할 수 있다는 것을 보여줍니다. 이를 통해 ANN이 SNN의 에너지 효율성을 실현합니다. MNIST 추론 문제를 다층 퍼셉트론을 사용하여 96%의 정확도로 처리하고, 10개의 Shenjing 코어만으로 1.26mW의 전력을 소모했습니다.