A-Graph: A Unified Graph Representation for At-Will Simulation across System Stacks

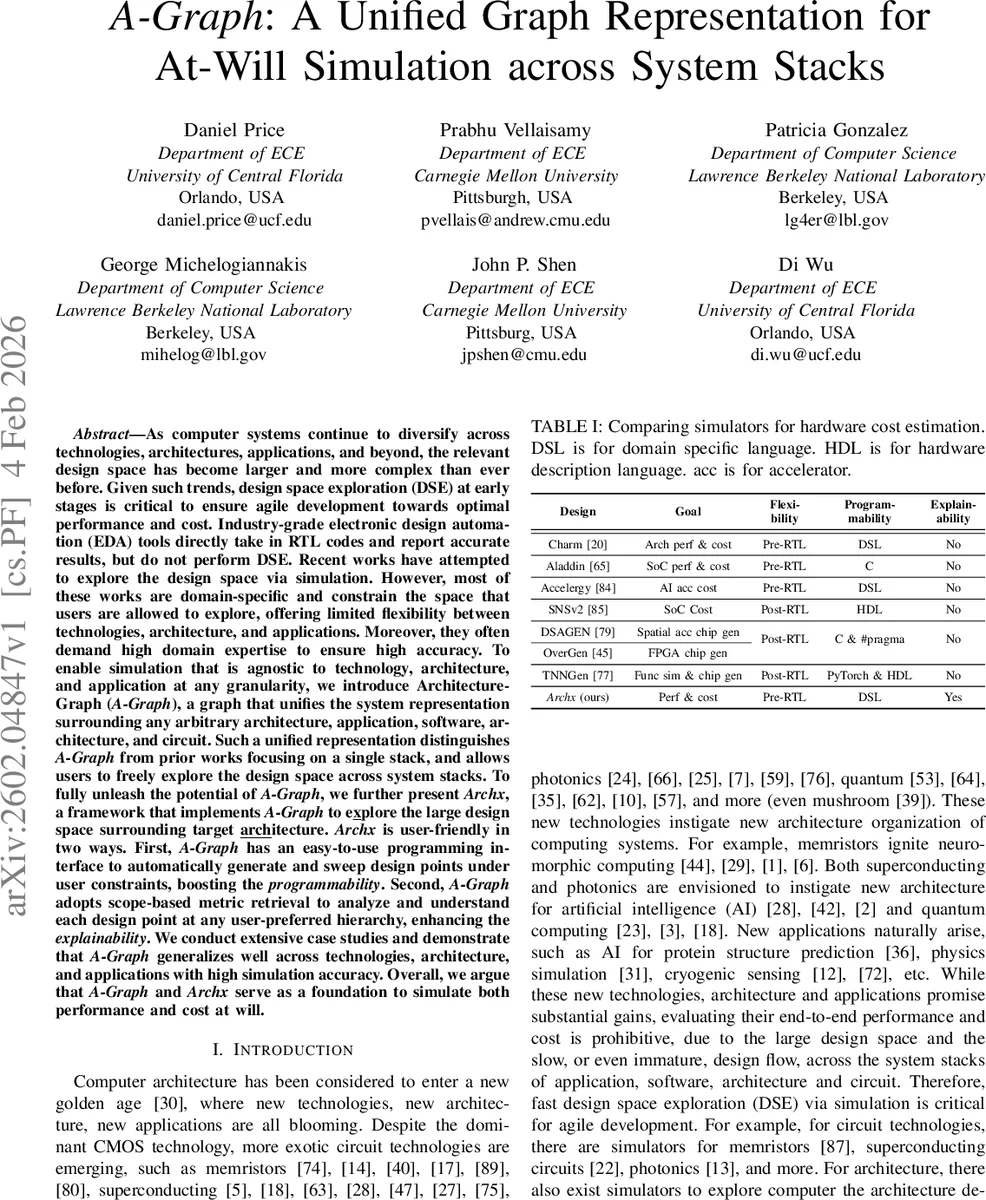

As computer systems continue to diversify across technologies, architectures, applications, and beyond, the relevant design space has become larger and more complex. Given such trends, design space exploration (DSE) at early stages is critical to ensure agile development towards optimal performance and cost. Industry-grade EDA tools directly take in RTL code and report accurate results, but do not perform DSE. Recent works have attempted to explore the design space via simulation. However, most of these works are domain-specific and constrain the space that users are allowed to explore, offering limited flexibility between technologies, architecture, and applications. Moreover, they often demand high domain expertise to ensure high accuracy. To enable simulation that is agnostic to technology, architecture, and application at any granularity, we introduce Architecture-Graph (Agraph), a graph that unifies the system representation surrounding any arbitrary application, software, architecture, and circuit. Such a unified representation distinguishes Agraph from prior works, which focus on a single stack, allowing users to freely explore the design space across system stacks. To fully unleash the potential of Agraph, we further present Archx, a framework that implements Agraph. Archx is user-friendly in two ways. First, Archx has an easy-to-use programming interface to automatically generate and sweep design points under user constraints, boosting the programmability. Second, Archx adopts scope-based metric retrieval to analyze and understand each design point at any user-preferred hierarchy, enhancing the explainability. We conduct case studies that demonstrate Agraph’s generalization across technologies, architecture, and applications with high simulation accuracy. Overall, we argue that Agraph and Archx serve as a foundation to simulate both performance and cost at will.

💡 Research Summary

The paper addresses the growing complexity of modern computing systems, where emerging device technologies (e.g., memristors, superconducting SFQ, photonics), novel architectures (binary, neuromorphic, quantum‑inspired), and diverse applications (AI, signal processing, robotics) create an enormous design space that must be explored early in the development cycle. Traditional electronic design automation (EDA) tools provide accurate post‑silicon power‑performance‑area (PPA) estimates from RTL, but they do not support rapid design‑space exploration (DSE). Existing simulators are either domain‑specific, limited to a single stack (application, software, architecture, or circuit), or require deep expertise to achieve acceptable accuracy. Consequently, designers lack a unified, flexible, and explainable framework that can evaluate performance and cost across all stacks at arbitrary granularity.

To fill this gap, the authors propose Architecture‑Graph (A‑Graph), a weighted directed acyclic graph (WDAG) that simultaneously models events and dependencies across four abstraction layers: application, software, architecture, and circuit. Nodes represent system events (e.g., a GEMM operation, a spike‑processing step), while weighted edges encode how many sub‑events, data transfers, or computational operations each parent event entails. By vertically decomposing the system and flattening inter‑stack dependencies into a single graph, A‑Graph enables “at‑will” simulation: users can choose any granularity—from high‑level algorithmic models to cycle‑accurate RTL or even SPICE‑level circuit models—without changing the underlying representation. The acyclic nature guarantees a deterministic topological order for metric aggregation, and the weighted edges allow complex composite operations (e.g., a MAC comprising multiple multiplications and additions) to be captured succinctly.

Building on A‑Graph, the authors introduce Archx, a software framework that (1) provides a domain‑specific language‑like programming interface for constructing the graph, (2) automatically generates design points that satisfy user‑specified constraints (e.g., power budget, technology choice), and (3) performs scope‑based metric retrieval. The scope mechanism lets users query metrics at any hierarchical level—system‑wide, subsystem, module, or individual circuit—facilitating rapid “what‑if” analysis and improving explainability. Archx also abstracts metric definitions, allowing custom units (e.g., mm² for CMOS area, number of Josephson Junctions for superconducting area) and custom performance models per event.

The paper validates the approach with four case studies spanning two technologies (CMOS and superconducting SFQ), two architectural paradigms (binary and neuromorphic), and two application domains (signal‑processing kernels and GEMM). Compared against industry‑grade RTL‑based EDA flows, Archx achieves performance and area estimates within 5‑10 % error while reducing simulation time from hours to seconds. In the superconducting case, Archx correctly reports area in terms of JJ count and power in femtowatts, metrics that conventional tools do not natively provide. These results demonstrate that A‑Graph can faithfully capture cross‑stack behavior while offering orders‑of‑magnitude speed‑up.

Key insights include:

- Unified representation eliminates the need for separate simulators per stack, enabling co‑design across technology, architecture, and application.

- Weighted dependency modeling captures both spatial and temporal relationships through event‑level performance models, preserving accuracy without requiring full RTL implementation.

- Scope‑based metric extraction dramatically improves explainability, allowing designers to pinpoint bottlenecks at the desired abstraction level.

- Programmable constraint‑driven exploration reduces manual effort and prevents blind exhaustive searches, making DSE accessible to non‑experts.

In conclusion, A‑Graph and its implementation Archx constitute a foundational platform for “at‑will” simulation of performance and cost across heterogeneous system stacks. By unifying representation, providing flexible granularity, and delivering explainable metrics, the framework empowers rapid, accurate DSE for emerging computing paradigms. Future work may extend automatic graph generation from high‑level code, integrate machine‑learning‑guided design point selection, and broaden support to additional emerging technologies such as photonic and quantum devices.

Comments & Academic Discussion

Loading comments...

Leave a Comment