Towards Pixel-Wise Anomaly Location for High-Resolution PCBA via Self-Supervised Image Reconstruction

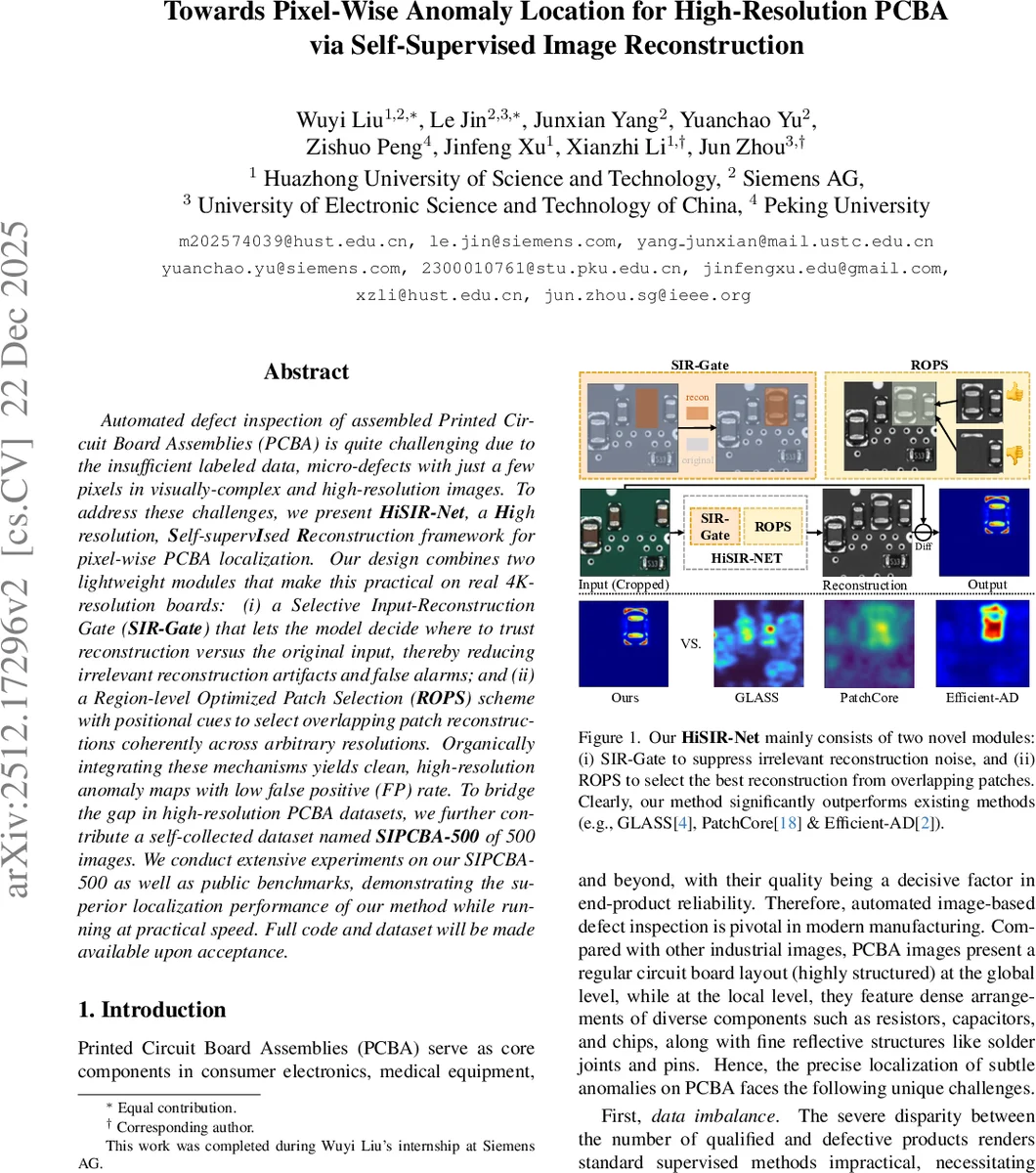

Automated defect inspection of assembled Printed Circuit Board Assemblies (PCBA) is quite challenging due to the insufficient labeled data, micro-defects with just a few pixels in visually-complex and high-resolution images. To address these challenges, we present HiSIR-Net, a High resolution, Self-supervised Reconstruction framework for pixel-wise PCBA localization. Our design combines two lightweight modules that make this practical on real 4K-resolution boards: (i) a Selective Input-Reconstruction Gate (SIR-Gate) that lets the model decide where to trust reconstruction versus the original input, thereby reducing irrelevant reconstruction artifacts and false alarms; and (ii) a Region-level Optimized Patch Selection (ROPS) scheme with positional cues to select overlapping patch reconstructions coherently across arbitrary resolutions. Organically integrating these mechanisms yields clean, high-resolution anomaly maps with low false positive (FP) rate. To bridge the gap in high-resolution PCBA datasets, we further contribute a self-collected dataset named SIPCBA-500 of 500 images. We conduct extensive experiments on our SIPCBA-500 as well as public benchmarks, demonstrating the superior localization performance of our method while running at practical speed. Full code and dataset will be made available upon acceptance.

💡 Research Summary

The paper tackles the challenging problem of pixel‑wise defect localization on assembled printed circuit board assemblies (PCBA) captured at ultra‑high resolution (up to 4K). Conventional anomaly detection methods either require large labeled datasets, which are unavailable in industrial settings, or they suffer from severe false‑positive rates when dealing with micro‑defects that span only a few pixels. Moreover, directly applying existing reconstruction‑based or embedding‑based approaches to 4K images leads to prohibitive memory consumption and loss of sensitivity due to aggressive down‑sampling.

To address these issues, the authors propose HiSIR‑Net, a self‑supervised reconstruction framework specifically designed for high‑resolution PCBA inspection. The architecture consists of three main components: (1) a patch‑based encoder‑decoder that processes 128 × 128 patches to keep memory usage tractable; (2) a Selective Input‑Reconstruction Gate (SIR‑Gate) that learns a spatial mask indicating where to trust the reconstructed output versus the original input; and (3) a Region‑level Optimized Patch Selection (ROPS) module that merges overlapping patch reconstructions into a seamless full‑resolution image using positional encodings and a difference‑threshold based selection strategy.

Self‑Supervised Reconstruction.

During training, only normal (defect‑free) PCBA images are used. Each patch is augmented with random masking, geometric transforms, and pixel drops to simulate defects. The network is then forced to reconstruct the original clean patch from the corrupted version. The reconstruction loss combines mean‑squared error (MSE) and structural similarity (SSIM) to balance pixel‑level fidelity and perceptual quality. This encourages the model to learn a tight manifold of normal appearances; at inference time, any deviation between the input and its reconstruction is interpreted as an anomaly.

SIR‑Gate.

The encoder produces a latent representation Z that is fed into two parallel decoders: a reconstruction decoder and a mask decoder. The mask decoder predicts a gate M(Z) ∈

Comments & Academic Discussion

Loading comments...

Leave a Comment