Timing-Error Optimized Architecture for Current-Steering DACs

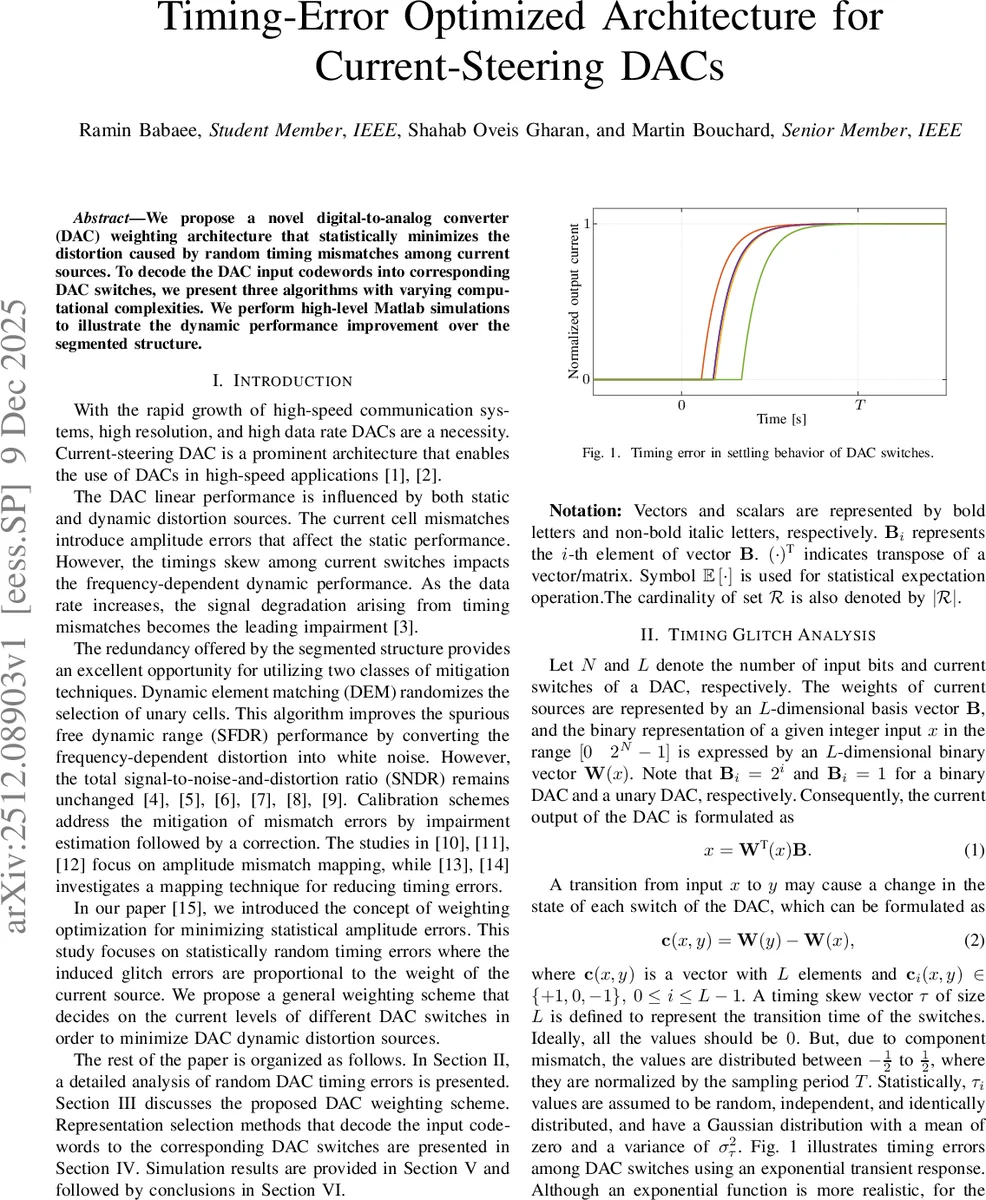

We propose a novel digital-to-analog converter (DAC) weighting architecture that statistically minimizes the distortion caused by random timing mismatches among current sources. To decode the DAC input codewords into corresponding DAC switches, we present three algorithms with varying computational complexities. We perform high-level Matlab simulations to illustrate the dynamic performance improvement over the segmented structure.

💡 Research Summary

The rapid advancement of high-speed communication and wideband signal processing systems has significantly increased the performance requirements for Digital-to-Analog Converters (DACs). Among various types, Current-Steering DACs are widely utilized in RF and high-speed data transmission due to their superior switching speed and driving capability. However, a critical bottleneck in these architectures is the signal distortion caused by random timing mismatches among the current sources. This timing error, often manifesting as jitter or skew, leads to non-linearities and the generation of unwanted spurs, thereby degrading the overall dynamic performance of the system.

This paper proposes a novel DAC weighting architecture specifically designed to statistically minimize the distortion induced by these random timing mismatches. Unlike the conventional segmented architecture, which divides bits into MSB and LSB sections based on a fixed pattern, the proposed architecture reconfigures the weighting of the current sources. The core innovation lies in the application of a statistical minimization strategy, where the weights are optimized to counteract the impact of timing errors on the signal’s linearity. By modeling the distribution of timing mismatches, the researchers have developed a method to redistribute the weights such that the resulting distortion energy is minimized.

To facilitate practical implementation, the paper introduces three distinct decoding algorithms, each offering a different level of computational complexity. This tiered approach provides hardware designers with a versatile design space to navigate the fundamental trade-offs between power consumption, silicon area, and signal integrity. The first algorithm is optimized for low-complexity, low-power applications where hardware resources are limited. The second algorithm provides a balanced performance-to-complexity ratio, while the third, most complex algorithm, is engineered for high-precision applications where maximizing dynamic range is the primary objective.

The effectiveness of the proposed architecture was validated through high-level Matlab simulations. The results demonstrate a significant improvement in dynamic performance metrics, such as Spurious-Free Dynamic Range (SFDR) and Signal-to-Noise and Distortion Ratio (SNDR), compared to the traditional segmented structure. The simulation data confirms that the proposed weighting architecture effectively mitigates the degradation caused by timing errors, maintaining high linearity even in the presence of stochastic mismatches. Ultimately, this research presents a powerful paradigm shift, demonstrating that architectural and algorithmic innovations can overcome the physical limitations of timing precision in modern semiconductor manufacturing, paving the way for next-generation high-speed DAC designs.

Comments & Academic Discussion

Loading comments...

Leave a Comment