Magnetic tunnel junction as a real-time entropy source: Field-Programmable Gate Array based random bit generation without post-processing

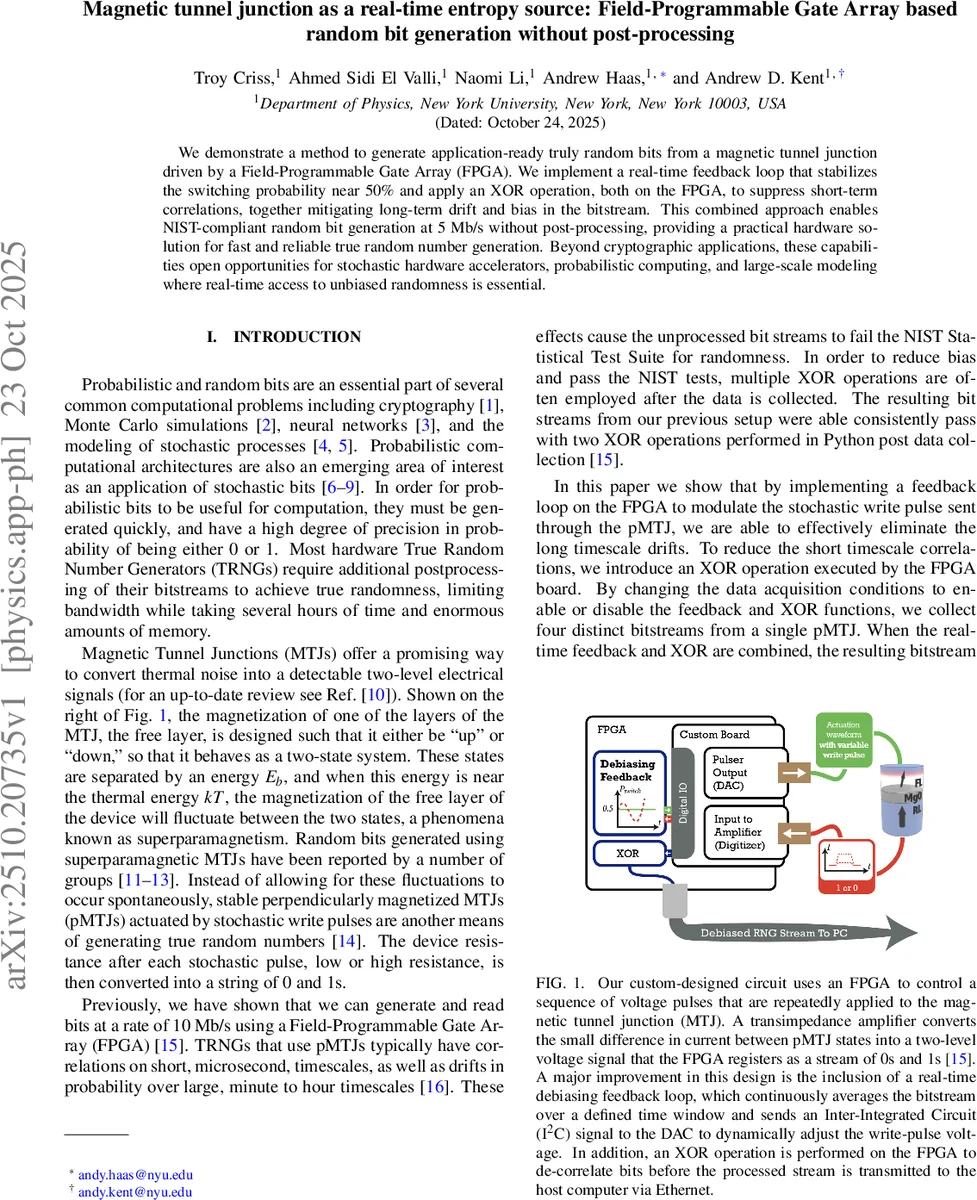

We demonstrate a method to generate application-ready truly random bits from a magnetic tunnel junction driven by a Field-Programmable Gate Array (FPGA). We implement a real-time feedback loop that stabilizes the switching probability near 50% and apply an XOR operation, both on the FPGA, to suppress short-term correlations, together mitigating long-term drift and bias in the bitstream. This combined approach enables NIST-compliant random bit generation at 5~Mb/s without post-processing, providing a practical hardware solution for fast and reliable true random number generation. Beyond cryptographic applications, these capabilities open opportunities for stochastic hardware accelerators, probabilistic computing, and large-scale modeling where real-time access to unbiased randomness is essential.

💡 Research Summary

The paper presents a hardware‑centric true random number generator (TRNG) that combines a magnetic tunnel junction (MTJ) with a field‑programmable gate array (FPGA) to produce unbiased random bits without any post‑processing. Traditional MTJ‑based TRNGs suffer from two major issues: short‑term correlations on the order of microseconds and long‑term drift of the switching probability over minutes to hours. Both effects cause raw bit streams to fail the NIST 800‑22 statistical test suite unless extensive offline processing (e.g., multiple XOR passes) is applied.

To address these problems, the authors implement two complementary techniques directly on the FPGA. First, a real‑time feedback loop monitors the average switching probability of the MTJ every second (i.e., after 10⁶ bits). The measured bias is compared to a target of 50 %. If the bias exceeds ±0.5 %, an I²C command adjusts the write‑pulse amplitude by one step of a 12‑bit DAC (≈0.44 mV). Because the experimentally determined slope near the 50 % point is dP/dV ≈ 1.6 % / mV, this fine‑grained voltage control can correct a probability shift of roughly 0.7 % per step, effectively suppressing low‑frequency drift.

Second, the FPGA performs an on‑board XOR operation to decorrelate bits. The authors discovered that XOR‑ing adjacent bits actually amplifies bias because consecutive MTJ outputs tend to be opposite. By storing bits in a circular buffer and XOR‑ing pairs separated by at least 4096 positions, short‑term correlations are eliminated without excessive memory usage. This separation was empirically determined to be sufficient for decorrelation.

Four data sets were collected from the same 50 nm pMTJ under different configurations: (1) no feedback, no XOR; (2) feedback only; (3) XOR only; (4) both feedback and XOR. Each set contains 10¹¹ bits (≈3 h of acquisition) sampled at 10.6 MHz (or 5.3 MHz after XOR). The results show:

- Without any mitigation, the switching probability drifts by 4–5 % over the experiment and exhibits 1–2 % short‑term fluctuations.

- Feedback alone stabilizes the probability near 50 % (variance σ² = 0.319) but leaves short‑term noise unchanged.

- XOR alone reduces short‑term variance (σ² = 1.01) but cannot correct the long‑term drift.

- Combining feedback and XOR yields the lowest variance (σ² = 0.051) and a stable 50 % probability.

Statistical validation includes histogramming 10⁵‑bit blocks and comparing the distribution to the expected binomial (normal) curve. Only the combined feedback‑XOR data matches the theoretical distribution within confidence limits. Power spectral density analysis further confirms that low‑frequency components (≤1 Hz) are suppressed when feedback is active.

Finally, the authors demonstrate that the combined scheme produces a continuous stream of random bits at an effective rate of 5 Mb/s (after a single XOR) that passes all NIST tests directly from the FPGA, eliminating the need for offline post‑processing. This achievement makes the device suitable for cryptographic key generation, stochastic hardware accelerators, probabilistic computing, and large‑scale Monte‑Carlo simulations where real‑time, high‑quality randomness is essential.

Comments & Academic Discussion

Loading comments...

Leave a Comment