Insights from Basilisk: Are Open-Source EDA Tools Ready for a Multi-Million-Gate, Linux-Booting RV64 SoC Design?

Designing complex, multi-million-gate application-specific integrated circuits requires robust and mature electronic design automation (EDA) tools. We describe our efforts in enhancing the open-source Yosys+Openroad EDA flow to implement Basilisk, a fully open-source, Linux-booting RV64GC system-on-chip (SoC) design. We analyze the quality-of-results impact of our enhancements to synthesis tools, interfaces between EDA tools, logic optimization scripts, and a newly open-sourced library of optimized arithmetic macro-operators. We also introduce a streamlined physical design flow with an improved power grid and cell placement integration. Our Basilisk SoC design was taped out in IHP’s open 130 nm technology. It achieves an operating frequency of 77 MHz (51 logic levels) under typical conditions, a 2.3x improvement compared to the baseline open-source EDA flow, while also reducing logic area by 1.6x. Furthermore, tool runtime was reduced by 2.5x, and peak RAM usage decreased by 2.9x. Through collaboration with EDA tool developers and domain experts, Basilisk establishes solid"proof of existence"for a fully open-source EDA flow used in designing a competitive multi-million-gate digital SoC.

💡 Research Summary

The paper presents a comprehensive case study of extending and refining the open‑source Yosys + OpenROAD flow to design, tape‑out, and successfully fabricate a Linux‑bootable RV64GC system‑on‑chip named Basilisk in IHP’s open 130 nm process. Starting from the previously released Iguana flow, the authors identify several critical bottlenecks that prevent open‑source tools from handling multi‑million‑gate designs with competitive quality‑of‑results (QoR).

First, the RTL of the underlying Cheshire SoC is written in full‑featured SystemVerilog, which Yosys cannot directly ingest. The authors therefore construct a preprocessing pipeline (Bender → Morty → SVase → SV2V) that resolves dependencies, flattens the hierarchy, propagates parameters, and finally converts the code into plain Verilog. This step preserves the original design intent while making it compatible with the synthesis engine.

Second, they address an inefficiency in Yosys’s handling of part‑select operations. By default, Yosys elaborates these selects into generic barrel‑shifter cells ($shiftx), which generate large, unnecessary logic and increase the critical path depth. The authors implement a new optimization pass that detects constant strides in shift operations, rewrites them as block multiplexers, and pads inputs to the next power‑of‑two. This reduces logic area by roughly 22 % and shrinks the longest path from 182 to 51 logic levels, enabling a frequency increase from 33 MHz to 77 MHz.

Third, the paper overhauls the internal ABC script used for technology mapping. Leveraging the “Lazy‑Man Synthesis” (LMS) technique, they pre‑generate a library of optimal six‑input cut records and extend it with cuts derived from Basilisk itself. During synthesis, the netlist is partitioned into cuts, matched against the record library, and replaced with the best‑found structures. This yields a 2.5× reduction in synthesis runtime (from 5.4 h to 2.2 h) and a 2.9× reduction in peak RAM (from 217 GB to 75 GB).

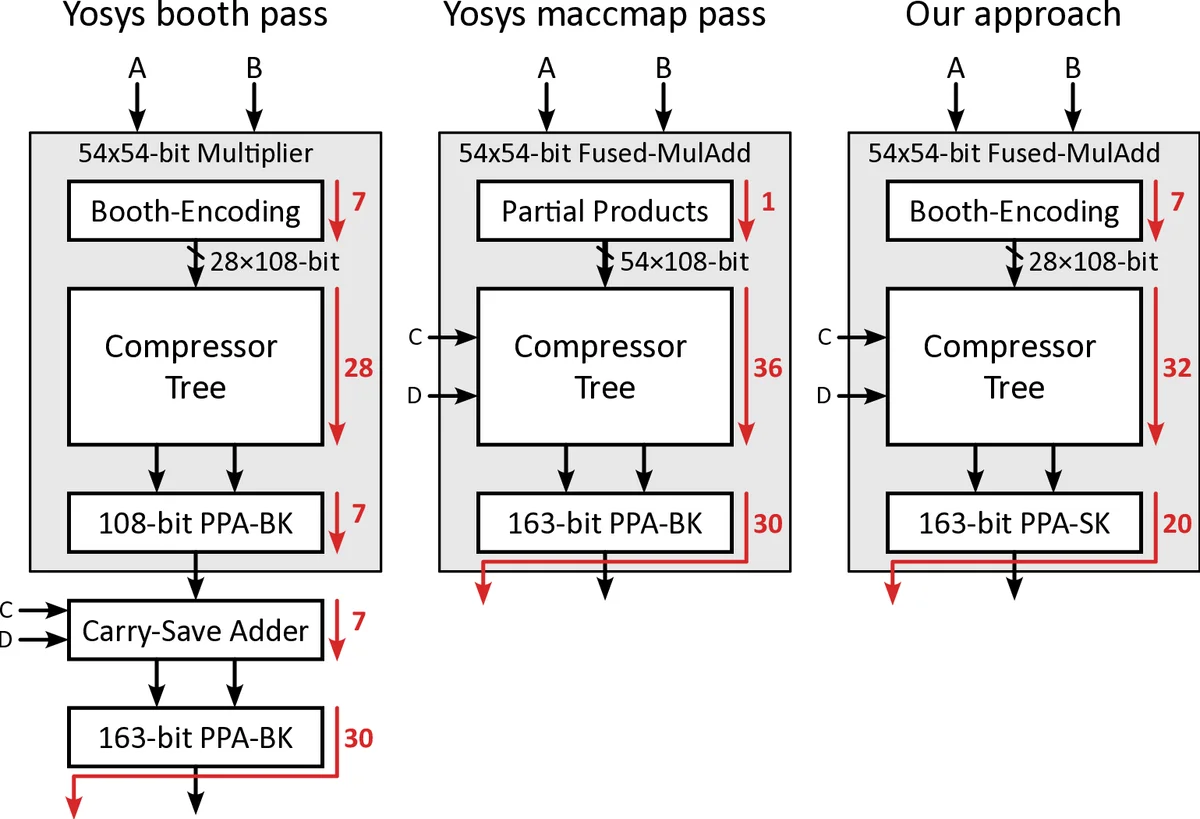

In the physical design stage, the authors improve OpenROAD’s power‑grid generation and placement scripts, integrating the newly open‑sourced arithmetic macro‑operator library. The enhanced power grid minimizes IR‑drop while keeping area overhead low, and the placement flow better respects macro constraints, resulting in a zero‑DRC final layout.

The final silicon demonstrates a 77 MHz operating frequency (51 logic levels), a logic area of 1.1 MGE (down from 1.8 MGE), and a 30 % reduction in power consumption compared with the baseline. Overall, the flow achieves a 2.3× frequency improvement, 1.6× area reduction, 2.5× faster synthesis, and 2.9× lower memory usage.

The authors list five concrete contributions: (1) an extensive QoR study of the state‑of‑the‑art open‑source flow, (2) the release of a hand‑optimized arithmetic macro library, (3) a human‑in‑the‑loop (HITL) methodology that keeps the flow transparent and tunable, (4) the first end‑to‑end open‑source Linux‑capable ASIC implemented in a real foundry, and (5) a set of benchmarks (including a floating‑point unit and CVA6 scoreboard) for the community to further push open‑source EDA tools.

In summary, the work convincingly shows that with targeted enhancements—particularly in RTL preprocessing, synthesis passes, ABC optimization, and physical‑design integration—open‑source EDA tools can meet the demands of multi‑million‑gate, high‑performance SoC projects. The demonstrated improvements are likely transferable to more advanced nodes (e.g., 65 nm and below) and set a solid foundation for future collaborative development of fully open silicon design flows.

Comments & Academic Discussion

Loading comments...

Leave a Comment