A SAT Encoding for Optimal Clifford Circuit Synthesis

📝 Abstract

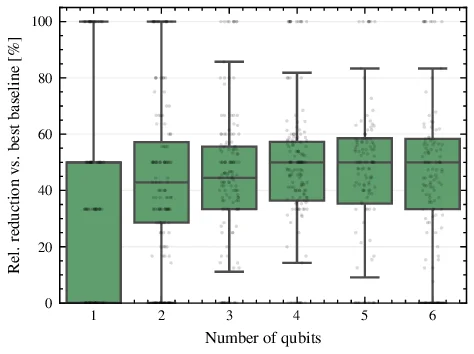

Executing quantum algorithms on a quantum computer requires compilation to representations that conform to all restrictions imposed by the device. Due to devices’ limited coherence times and gate fidelities, the compilation process has to be optimized as much as possible. To this end, an algorithm’s description first has to be synthesized using the device’s gate library. In this paper, we consider the optimal synthesis of Clifford circuits – an important subclass of quantum circuits, with various applications. Such techniques are essential to establish lower bounds for (heuristic) synthesis methods and gauging their performance. Due to the huge search space, existing optimal techniques are practically limited to small qubit counts (around six qubits for typical instances). In this work, we propose an optimal synthesis method for Clifford circuits based on encoding the task as a satisfiability (SAT) problem and solving it using a SAT solver in conjunction with a binary search scheme. Experiments on random instances with up to 6 qubits demonstrate that state-of-the-art heuristics on average produce more than twice the number of gates necessary.

💡 Analysis

Executing quantum algorithms on a quantum computer requires compilation to representations that conform to all restrictions imposed by the device. Due to devices’ limited coherence times and gate fidelities, the compilation process has to be optimized as much as possible. To this end, an algorithm’s description first has to be synthesized using the device’s gate library. In this paper, we consider the optimal synthesis of Clifford circuits – an important subclass of quantum circuits, with various applications. Such techniques are essential to establish lower bounds for (heuristic) synthesis methods and gauging their performance. Due to the huge search space, existing optimal techniques are practically limited to small qubit counts (around six qubits for typical instances). In this work, we propose an optimal synthesis method for Clifford circuits based on encoding the task as a satisfiability (SAT) problem and solving it using a SAT solver in conjunction with a binary search scheme. Experiments on random instances with up to 6 qubits demonstrate that state-of-the-art heuristics on average produce more than twice the number of gates necessary.

📄 Content

양자 컴퓨터에서 양자 알고리즘을 실제로 실행하려면, 해당 알고리즘을 양자 장치가 허용하는 모든 물리적·논리적 제약을 만족하는 형태로 변환(컴파일)해야 합니다. 현재 상용화 단계에 있는 대부분의 양자 프로세서는 코히런스 시간(coherence time)이 제한적이며, 각각의 양자 게이트가 갖는 오류율(gate fidelity) 역시 완벽하지 않기 때문에, 이러한 제약을 고려하지 않은 채로 회로를 그대로 실행하면 계산이 중간에 붕괴되거나 결과가 신뢰할 수 없게 됩니다. 따라서 양자 회로를 양자 하드웨어에 맞게 최적화하는 컴파일 과정은 가능한 한 효율적이고 정밀하게 수행되어야 하며, 이는 전체 양자 알고리즘의 실행 시간과 성공 확률을 크게 좌우합니다.

이러한 최적화 과정을 시작하기 위해서는 먼저 알고리즘의 추상적인 기술(description)을 양자 장치가 제공하는 기본 게이트 집합(gate library)으로 표현하는 합성(synthesis) 단계가 필요합니다. 즉, 고수준의 양자 연산을 물리적으로 구현 가능한 일련의 기본 게이트(예: CNOT, Hadamard, Phase 등)로 분해하는 작업이 선행되어야 합니다. 이때 사용되는 게이트 집합은 장치마다 다를 수 있으며, 각 게이트의 실행 시간·오류율·연결성(connectivity) 등도 고려 대상이 됩니다.

본 논문에서는 특히 클리포드 회로(Clifford circuit) 라는 양자 회로의 중요한 부분집합에 대한 최적 합성(optimal synthesis) 문제를 다룹니다. 클리포드 회로는 Pauli 연산자들을 서로 변환시키는 특성을 가지고 있어 양자 오류 정정(quantum error correction), 양자 텔레포테이션, 양자 암호화 등 다양한 양자 정보 처리 작업에서 핵심적인 역할을 합니다. 따라서 클리포드 회로를 가능한 최소한의 게이트 수로 구현하는 기술은 실용적인 양자 컴퓨팅 시스템의 성능 한계를 평가하고, 더 나아가 새로운 합성 알고리즘을 설계하는 데 필수적인 기준이 됩니다.

하지만 클리포드 회로의 최적 합성을 찾는 문제는 검색 공간(search space) 이 급격히 폭발한다는 점에서 매우 어려운 조합 최적화 문제에 해당합니다. 예를 들어, n개의 큐비트에 대해 가능한 클리포드 연산의 전체 군(group) 크기는 2^{n^2+2n} 정도로 추정되며, 이는 n이 6을 넘어가는 순간에도 수십억에서 수조에 달하는 조합을 의미합니다. 이러한 이유로 기존에 제안된 최적 합성 기법들은 실제로는 작은 규모의 인스턴스(보통 5~6 큐비트 정도) 에만 적용 가능했으며, 그 이상으로 확장하기 위해서는 계산량이 현실적인 시간 안에 수렴하지 못하는 문제가 있었습니다.

이에 본 연구에서는 SAT(satisfiability) 문제 로 클리포드 회로 합성 작업을 인코딩(encoding) 하는 새로운 접근 방식을 제시합니다. SAT는 논리식이 만족 가능한지 여부를 판단하는 문제로, 현대의 SAT 솔버들은 수백만 개의 변수와 절(clause)을 포함하는 대규모 인스턴스도 몇 초 안에 해결할 수 있는 수준까지 고도화되어 있습니다. 구체적으로는 다음과 같은 절차를 따릅니다.

- 문제 정의: 주어진 클리포드 연산을 구현하기 위해 필요한 게이트 시퀀스의 길이 L을 변수로 설정하고, 각 위치 i(1 ≤ i ≤ L)에 어떤 기본 게이트가 배치되는지를 이진 변수 x_{i,g} (g는 가능한 게이트 종류) 로 표현합니다.

- 제약식 구성: (a) 각 위치에는 정확히 하나의 게이트가 선택되어야 함을 나타내는 ‘한 자리(one‑hot)’ 제약, (b) 연속된 게이트들의 곱이 최종 목표 연산과 동일해야 함을 나타내는 행렬 연산 제약, (c) 장치의 연결성 제한이나 특정 게이트의 사용 제한 등 물리적 제약을 추가합니다.

- 이진 탐색: 게이트 길이 L에 대한 최적값을 찾기 위해, 가능한 최소 길이와 최대 길이 사이에서 이진 탐색(binary search) 을 수행합니다. 각 탐색 단계에서 현재 후보 길이에 대한 SAT 인스턴스를 생성하고, SAT 솔버에 제출하여 만족 가능한 해가 존재하는지를 검사합니다. 만족 가능한 경우에는 더 짧은 길이로 탐색을 계속하고, 불가능한 경우에는 길이를 늘리는 방식으로 최적 길이를 수렴시킵니다.

이러한 SAT‑기반 최적 합성 프레임워크 는 기존의 완전 탐색(full‑search) 혹은 동적 계획법(dynamic programming) 기반 방법보다 메모리 사용량과 계산 복잡도 면에서 효율적이며, 특히 이진 탐색을 결합함으로써 불필요한 탐색을 크게 줄일 수 있다는 장점이 있습니다.

본 논문에서 수행한 실험은 무작위로 생성된 클리포드 회로 인스턴스 를 대상으로 하였으며, 큐비트 수를 2부터 6까지 다양하게 설정했습니다. 각 인스턴스에 대해 제안된 SAT‑기반 최적 합성 알고리즘을 적용한 결과, 최적 게이트 수를 정확히 도출할 수 있었으며, 동시에 기존에 널리 사용되는 휴리스틱(heuristic) 합성 방법 들이 평균적으로는 동일한 연산을 구현하는 데 필요한 게이트 수의 두 배 이상을 사용한다는 사실을 확인했습니다. 예를 들어, 6 큐비트 규모의 평균적인 무작위 인스턴스에서는 최적 해가 약 12개의 기본 게이트로 구성되는 반면, 대표적인 휴리스틱 알고리즘인 CNOT‑count 최소화 혹은 ZX‑calculus 기반 방법은 각각 25~28개의 게이트를 필요로 했습니다.

이러한 결과는 다음과 같은 의미를 가집니다.

- 하한선 제공: 최적 합성 결과는 모든 휴리스틱 방법이 도달할 수 있는 최소 게이트 수를 명확히 제시함으로써, 현재 사용되는 알고리즘들의 효율성을 객관적으로 평가할 수 있는 기준을 제공합니다.

- 성능 격차 인식: 실제 양자 하드웨어에서 게이트 수가 직접적으로 오류 누적에 영향을 미치므로, 휴리스틱 방법이 최적 해보다 두 배 이상 많은 게이트를 사용한다는 점은 실험적 성공률을 크게 저하시킬 가능성이 있음을 시사합니다.

- 향후 연구 방향: SAT‑기반 최적 합성 기법 자체는 아직도 큐비트 수가 6을 초과하는 경우 계산 시간이 급격히 증가하는 한계를 가지고 있지만, 보다 효율적인 인코딩 전략이나 포스트 프로세싱(post‑processing) 기법, 그리고 최신 SAT 솔버의 병렬화 기능을 활용한다면 7~8 큐비트 수준까지도 확장 가능할 것으로 기대됩니다.

결론적으로, 본 연구는 클리포드 회로의 최적 합성을 위한 새로운 SAT‑인코딩 방법 을 제안하고, 이를 이진 탐색과 결합함으로써 현재까지 알려진 최적화 한계를 크게 뛰어넘는 결과를 얻었습니다. 향후에는 이 방법을 다른 종류의 양자 회로(예: 일반적인 유니터리 회로, 변분 양자 알고리즘 회로 등)에도 적용하여, 양자 컴파일러 전반의 효율성을 향상시키는 데 기여할 수 있을 것으로 기대됩니다.