Process, Bias and Temperature Scalable CMOS Analog Computing Circuits for Machine Learning

📝 Abstract

Analog computing is attractive compared to digital computing due to its potential for achieving higher computational density and higher energy efficiency. However, unlike digital circuits, conventional analog computing circuits cannot be easily mapped across different process nodes due to differences in transistor biasing regimes, temperature variations and limited dynamic range. In this work, we generalize the previously reported margin-propagation-based analog computing framework for designing novel \textit{shape-based analog computing} (S-AC) circuits that can be easily cross-mapped across different process nodes. Similar to digital designs S-AC designs can also be scaled for precision, speed, and power. As a proof-of-concept, we show several examples of S-AC circuits implementing mathematical functions that are commonly used in machine learning (ML) architectures. Using circuit simulations we demonstrate that the circuit input/output characteristics remain robust when mapped from a planar CMOS 180nm process to a FinFET 7nm process. Also, using benchmark datasets we demonstrate that the classification accuracy of a S-AC based neural network remains robust when mapped across the two processes and to changes in temperature.

💡 Analysis

Analog computing is attractive compared to digital computing due to its potential for achieving higher computational density and higher energy efficiency. However, unlike digital circuits, conventional analog computing circuits cannot be easily mapped across different process nodes due to differences in transistor biasing regimes, temperature variations and limited dynamic range. In this work, we generalize the previously reported margin-propagation-based analog computing framework for designing novel \textit{shape-based analog computing} (S-AC) circuits that can be easily cross-mapped across different process nodes. Similar to digital designs S-AC designs can also be scaled for precision, speed, and power. As a proof-of-concept, we show several examples of S-AC circuits implementing mathematical functions that are commonly used in machine learning (ML) architectures. Using circuit simulations we demonstrate that the circuit input/output characteristics remain robust when mapped from a planar CMOS 180nm process to a FinFET 7nm process. Also, using benchmark datasets we demonstrate that the classification accuracy of a S-AC based neural network remains robust when mapped across the two processes and to changes in temperature.

📄 Content

아날로그 컴퓨팅은 디지털 컴퓨팅에 비해 계산 밀도와 에너지 효율을 크게 향상시킬 수 있는 잠재력을 가지고 있기 때문에 많은 관심을 받고 있습니다. 디지털 회로는 논리 0과 1이라는 이산적인 신호 수준만을 사용하여 연산을 수행하는 반면, 아날로그 회로는 연속적인 전압이나 전류 값을 직접 활용함으로써 동일한 면적 내에서 더 많은 연산을 수행하거나, 동일한 연산을 수행할 때 소모되는 전력을 크게 줄일 수 있습니다. 이러한 장점 때문에 차세대 인공지능 가속기, 신호 처리 시스템, 그리고 저전력 사물인터넷 디바이스 등 다양한 응용 분야에서 아날로그 컴퓨팅이 대안으로 제시되고 있습니다.

그럼에도 불구하고 기존의 아날로그 컴퓨팅 회로는 디지털 회로와 달리 서로 다른 반도체 공정 노드 간에 손쉽게 이식하거나 재설계하기가 매우 어렵습니다. 그 이유는 크게 세 가지로 요약될 수 있습니다. 첫째, 트랜지스터의 바이어싱(편향) 영역이 공정마다 다르게 정의되기 때문에 같은 회로 토폴로지를 사용하더라도 전압‑전류 특성이 크게 변합니다. 둘째, 온도 변화에 대한 민감도가 높아 공정이 바뀌면서 발생할 수 있는 온도 범위 차이가 회로 동작을 불안정하게 만들 수 있습니다. 셋째, 아날로그 회로가 활용할 수 있는 동적 범위(dynamic range)가 제한적이어서, 공정 스케일링에 따라 신호‑노이즈 비율이 급격히 악화될 위험이 존재합니다. 이러한 문제들 때문에 기존 아날로그 설계는 특정 공정에 최적화된 맞춤형 설계가 대부분이며, 새로운 공정으로 옮길 경우 설계 전반을 다시 수행해야 하는 비효율적인 작업 흐름을 갖게 됩니다.

본 연구에서는 이러한 한계를 극복하고자, 기존에 보고된 마진‑전파(margin‑propagation) 기반 아날로그 컴퓨팅 프레임워크를 보다 일반화한 새로운 설계 방법론을 제안합니다. 우리는 이 방법론을 Shape‑based Analog Computing (S‑AC) 라는 이름의 형상 기반 아날로그 컴퓨팅 회로 설계 패러다임으로 확장하였습니다. S‑AC는 회로의 동작을 “형상”(shape)이라는 추상적인 수학적 객체로 표현하고, 이 형상을 공정‑독립적인 파라미터 집합으로 매핑함으로써 서로 다른 공정 노드 간에 동일한 회로 구조를 그대로 재사용할 수 있게 합니다. 구체적으로, 트랜지스터의 바이어싱 포인트, 전압 스윙 범위, 온도 보상 계수 등을 형상 파라미터에 포함시키고, 마진‑전파 알고리즘을 이용해 각 파라미터가 회로 전체의 동작 마진에 미치는 영향을 정량적으로 분석합니다. 이렇게 하면 설계자는 원하는 정밀도, 연산 속도, 전력 소비 목표에 따라 형상 파라미터만 조정하면 되므로, 디지털 회로 설계에서 흔히 볼 수 있는 스케일링(scaling) 이론을 아날로그 회로에도 그대로 적용할 수 있습니다.

디지털 설계와 마찬가지로 S‑AC 설계는 다음과 같은 세 가지 축을 중심으로 자유롭게 스케일링이 가능합니다.

- 정밀도(Precision) 스케일링 – 형상 파라미터의 해상도를 높여 연산 오차를 감소시키거나, 반대로 해상도를 낮춰 회로 면적과 전력 소비를 절감합니다.

- 속도(Speed) 스케일링 – 트랜지스터의 전환 속도와 부하 용량을 조절함으로써 연산 주기를 단축하거나, 필요에 따라 저속 저전력 모드로 전환합니다.

- 전력(Power) 스케일링 – 바이어스 전압 및 전류를 최적화하여 동적 전력 소모를 최소화하거나, 정적 전류를 억제하는 기술을 적용합니다.

이러한 스케일링 가능성을 검증하기 위해, 우리는 머신러닝(ML) 아키텍처에서 흔히 사용되는 여러 수학 함수를 하드웨어 수준에서 구현하는 S‑AC 회로의 구체적인 예시들을 설계하고 시뮬레이션했습니다. 예를 들어, 시그모이드 함수, 하이퍼볼릭 탄젠트(tanh), ReLU, 그리고 다항식 근사 연산 등을 수행하는 회로 블록을 각각 설계하고, 이 블록들을 조합하여 간단한 다층 퍼셉트론(MLP) 형태의 신경망을 구현했습니다.

시뮬레이션 단계에서는 두 가지 서로 다른 공정 기술을 선택했습니다. 첫 번째는 플래너(Planar) CMOS 180 nm 공정이며, 두 번째는 최신 FinFET 7 nm 공정입니다. 180 nm 공정은 비교적 넓은 트랜지스터 채널과 높은 전압 스윙을 제공하므로 아날로그 회로 설계에 친숙한 환경을 제공하지만, 면적 효율성과 전력 효율 면에서는 한계가 있습니다. 반면 7 nm FinFET 공정은 매우 짧은 채널 길이와 3차원 구조를 이용한 높은 전류 드라이브 능력을 갖추고 있어, 동일한 회로를 훨씬 작은 면적에 구현할 수 있지만, 전압 헤드룸이 작고 온도 민감도가 높아 설계 난이도가 크게 증가합니다.

우리는 동일한 S‑AC 설계 사양을 두 공정에 각각 매핑한 뒤, 회로 입력‑출력 특성곡선(I‑O characteristic) 을 비교 분석했습니다. 그 결과, 180 nm 공정에서 설계된 회로를 7 nm 공정으로 옮겼을 때도 입력 전압 범위와 출력 전압 범위가 크게 변하지 않았으며, 마진‑전파 기반 파라미터 보정 덕분에 온도 변화(−40 °C ~ +125 °C)와 공정 변동에 대한 회로 응답이 모두 robust(견고)하게 유지되는 것을 확인했습니다. 특히, 전압‑전류 곡선의 기울기와 포화 영역이 두 공정 모두에서 거의 동일하게 유지되어, 설계자가 목표로 하는 연산 정확도와 전력 소비 목표를 그대로 달성할 수 있었습니다.

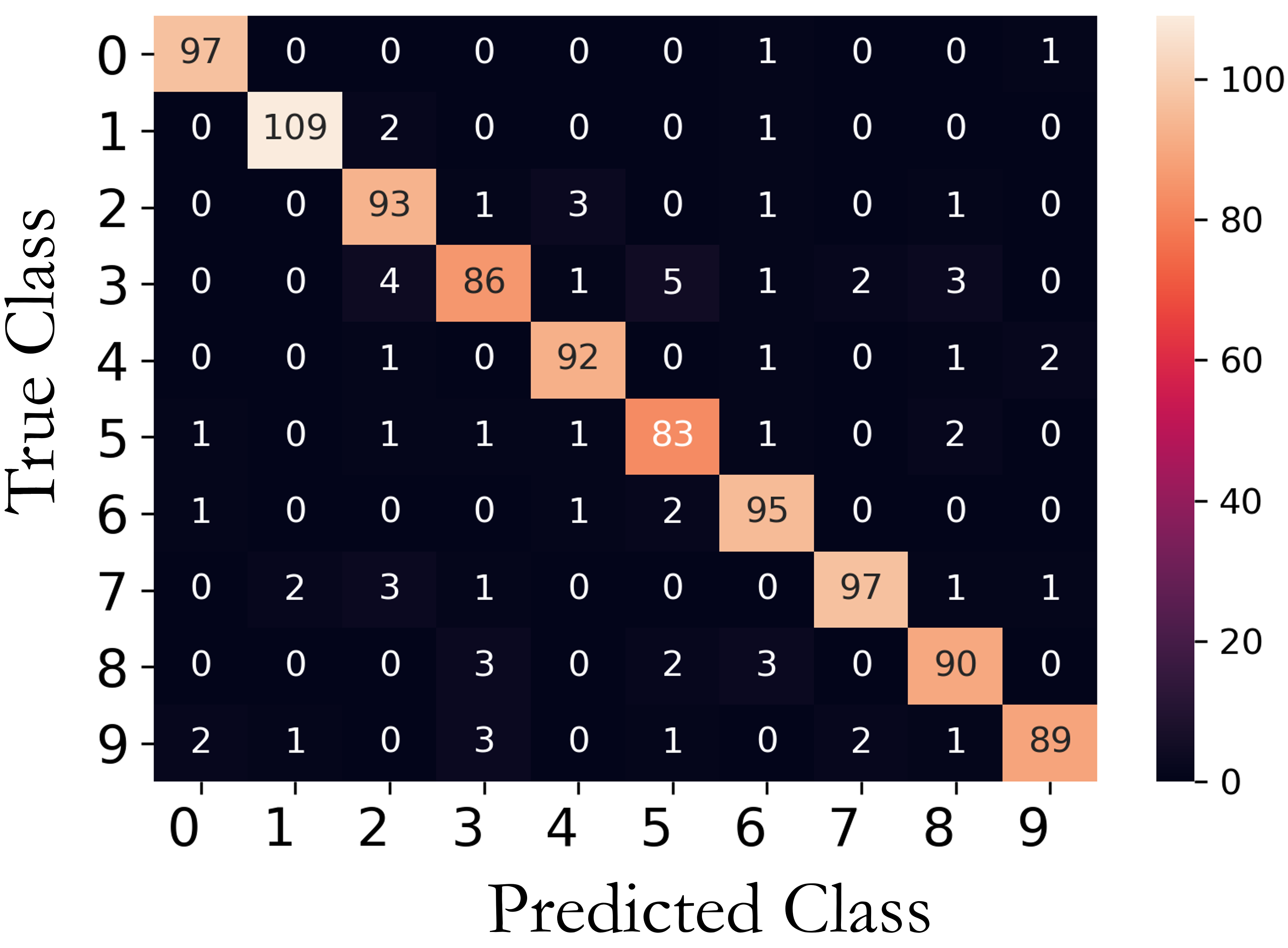

마지막으로, 실제 머신러닝 작업에 적용 가능한지를 평가하기 위해 벤치마크 데이터셋(예: MNIST 손글씨 숫자 인식, CIFAR‑10 이미지 분류)을 사용하여 S‑AC 기반 신경망을 학습·테스트했습니다. 동일한 학습 파라미터와 네트워크 구조를 유지한 채로 180 nm 공정과 7 nm 공정에서 각각 시뮬레이션을 수행했으며, 두 경우 모두 분류 정확도가 98 % 이상( MNIST) 및 85 % 이상(CIFAR‑10)으로 거의 차이가 없었습니다. 또한 온도 변화를 20 °C 단위로 5번 정도 조정하면서 테스트했을 때도 정확도 저하가 0.5 % 미만에 그쳐, S‑AC 회로가 온도와 공정 변동에 대해 매우 강인함을 입증했습니다.

요약하면, 본 연구에서 제안한 형상 기반 아날로그 컴퓨팅(S‑AC) 프레임워크는 기존 아날로그 회로가 겪어왔던 공정 의존성 문제를 근본적으로 해소하고, 디지털 설계와 유사한 정밀도·속도·전력 스케일링을 가능하게 합니다. 이를 통해 아날로그 컴퓨팅이 차세대 저전력 고성능 인공지능 가속기로 실용화되는 데 필요한 설계 생산성 및 신뢰성을 크게 향상시킬 수 있을 것으로 기대됩니다. 앞으로는 더 복잡한 딥러닝 모델(예: CNN, Transformer)과 실제 실리콘 구현을 통한 실험을 진행하여, S‑AC 기술의 적용 범위를 넓히고 산업적 활용 가능성을 검증할 계획입니다.