ArithsGen: Arithmetic Circuit Generator for Hardware Accelerators

Generators of arithmetic circuits can automatically deliver various implementations of arithmetic circuits that show different tradeoffs between the key circuit parameters (delay, area, power consumption). However, existing (freely-)available generators are limited if more complex circuits with a hierarchical structure and additional architecture optimization are requested. Furthermore, they support only a few output formats. In order to overcome the above-mentioned limitations, we developed a new generator of arithmetic circuits called ArithsGen. ArithsGen can generate specific architectures of signed and unsigned adders and multipliers using basic building elements such as wires and gates. Compared to existing generators, the user can, for example, specify the type of adders used in multipliers. The tool supports various outputs formats (Verilog, BLIF, C/C++, or integer netlists). ArithsGen was evaluated in the synthesis and optimization of generic customizable accurate and approximate adders and multipliers. Furthermore, we used the circuits generated by ArithsGen as seeds for a tool developed to automatically create approximate implementations of arithmetic circuits. We show that different initial circuits (generated by ArithsGen) significantly impact the properties of these approximate implementations. The tool is available online at https://github.com/ehw-fit/ariths-gen.

💡 Research Summary

The paper presents ArithsGen, a new open‑source generator for arithmetic circuits aimed at hardware accelerators such as neural‑network processors, image‑processing engines, and other data‑intensive ASICs or FPGAs. Existing generators (e.g., Arithmetic Module Generator, VHDLMultGenerator, GenMul) suffer from three major drawbacks: they are either abandoned, closed‑source, or hard‑wired to a limited set of architectures and output formats. ArithsGen addresses these issues by providing a Python‑based meta‑language that models wires, buses, logic gates, and higher‑level arithmetic blocks as classes. This object‑oriented approach enables hierarchical composition of circuits—from one‑bit half‑adders and full‑adders up to complex structures such as Dadda, Wallace, and array multipliers, as well as multiply‑and‑accumulate (MAC) units and approximate multipliers (broken‑array and truncated).

Key features of ArithsGen include:

-

Full configurability – Users can specify bit‑width, signed/unsigned representation, and the type of internal adder used in multipliers via simple constructor arguments (e.g.,

unsigned_adder_class_name). This allows the same top‑level multiplier to be instantiated with RCA, CLA, CSkA, or any user‑defined adder. -

Multiple output formats – The internal representation can be exported to Verilog, BLIF, C/C++ (for fast functional simulation), and the integer netlist format used by Cartesian Genetic Programming (CGP). Both hierarchical and flattened netlists are supported; flattening guarantees unique wire names and removes hierarchy for tools that cannot handle it.

-

Extensibility – Because every component is a Python class, new arithmetic blocks (e.g., floating‑point multipliers, logarithmic units) can be added by subclassing existing ones. The framework also allows substitution of library cells (e.g., technology‑specific full‑adders or multiplexers) without changing the higher‑level code.

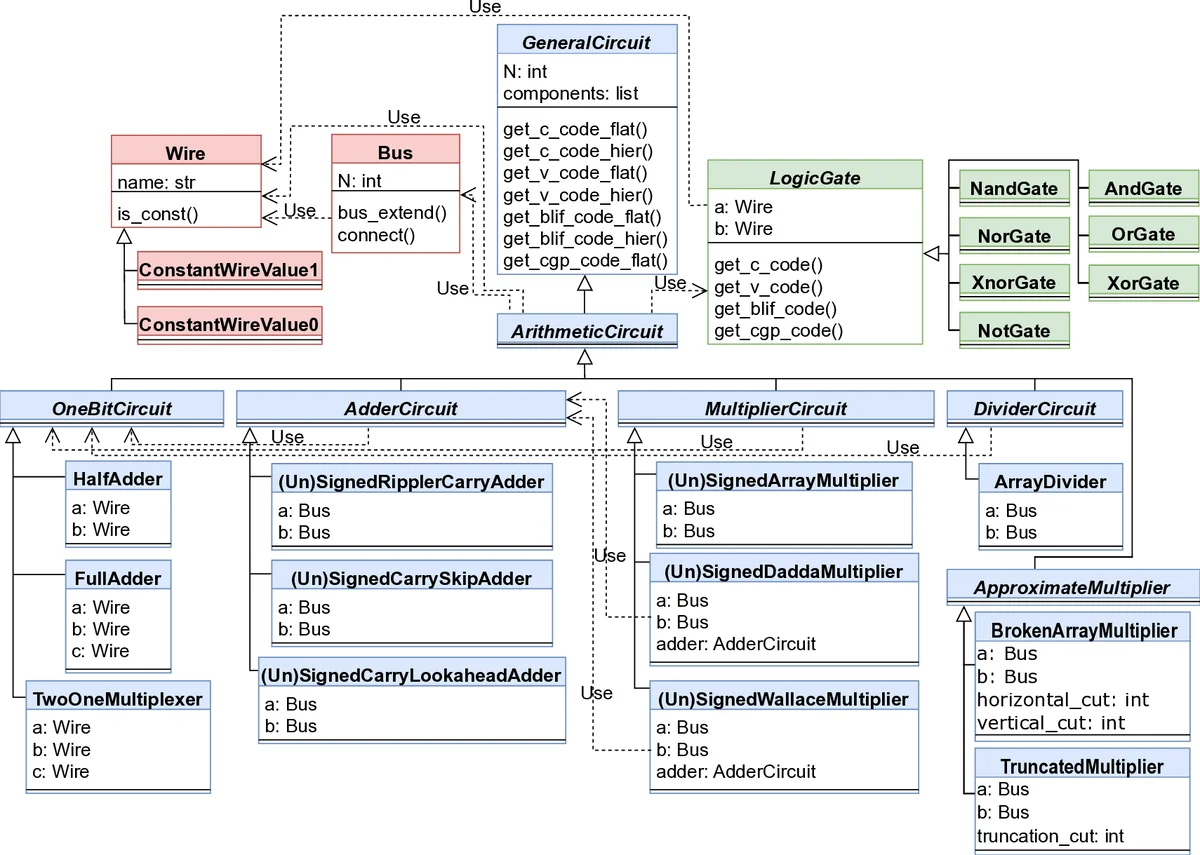

The implementation details are described through a class diagram: basic components (Wire, Bus, constant wires, various gate classes) form the foundation; one‑bit circuits (HalfAdder, FullAdder) are built from gates; complex circuits inherit from an abstract ArithmeticCircuit class and recursively instantiate lower‑level blocks. The generator automatically handles inter‑component wiring, bus truncation, and constant propagation, providing a modest amount of pre‑synthesis optimization before the downstream synthesis tool (e.g., Synopsys Design Compiler) performs full logic optimization.

Experimental validation is performed in two parts. First, functional correctness is verified using simulation for small designs and ABC for larger designs; 32‑bit circuits are generated in under 0.5 seconds, producing up to ~12 k lines of flat Verilog code. Second, a hardware‑accelerator scenario evaluates ASIC synthesis results using the FreePDK45 standard cell library with high‑effort delay optimization. The authors report that flattened adders achieve 25‑31 % lower power than hierarchical adders because the synthesis tool can better optimize a flat netlist. For multipliers, Dadda architectures provide about 10 % area reduction compared to a plain array multiplier, while power‑delay product varies with the choice of internal adder and error tolerance in approximate designs.

A further experiment uses the accurate circuits generated by ArithsGen as seeds for a CGP‑based approximate circuit generator (EvoApproxLib). The study shows that the initial exact circuit strongly influences the trade‑off space of the resulting approximate designs: different seed architectures lead to markedly different error, power, and area characteristics. This demonstrates the practical importance of having a flexible, high‑quality exact generator when exploring approximate arithmetic.

ArithsGen is released under an open‑source license on GitHub (https://github.com/ehw-fit/ariths-gen) together with a detailed tutorial and example scripts. The authors envision future extensions such as direct mapping to PDK‑specific cells, support for fixed‑point and floating‑point multipliers, and integration with machine‑learning‑driven design‑space exploration frameworks. In summary, ArithsGen fills a gap in the current ecosystem by offering a highly configurable, multi‑format, and extensible arithmetic circuit generator that can serve both as a rapid prototyping tool for accelerator designers and as a benchmark/seed source for formal verification and approximate computing research.

Comments & Academic Discussion

Loading comments...

Leave a Comment