On the Accuracy of Analog Neural Network Inference Accelerators

📝 Abstract

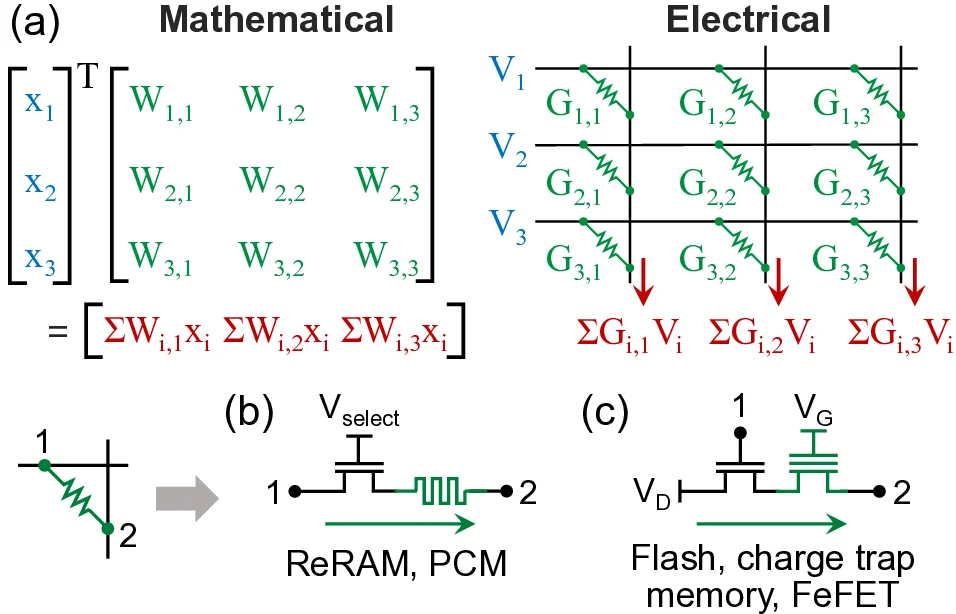

Specialized accelerators have recently garnered attention as a method to reduce the power consumption of neural network inference. A promising category of accelerators utilizes nonvolatile memory arrays to both store weights and perform $\textit{in situ}$ analog computation inside the array. While prior work has explored the design space of analog accelerators to optimize performance and energy efficiency, there is seldom a rigorous evaluation of the accuracy of these accelerators. This work shows how architectural design decisions, particularly in mapping neural network parameters to analog memory cells, influence inference accuracy. When evaluated using ResNet50 on ImageNet, the resilience of the system to analog non-idealities - cell programming errors, analog-to-digital converter resolution, and array parasitic resistances - all improve when analog quantities in the hardware are made proportional to the weights in the network. Moreover, contrary to the assumptions of prior work, nearly equivalent resilience to cell imprecision can be achieved by fully storing weights as analog quantities, rather than spreading weight bits across multiple devices, often referred to as bit slicing. By exploiting proportionality, analog system designers have the freedom to match the precision of the hardware to the needs of the algorithm, rather than attempting to guarantee the same level of precision in the intermediate results as an equivalent digital accelerator. This ultimately results in an analog accelerator that is more accurate, more robust to analog errors, and more energy-efficient.

💡 Analysis

Specialized accelerators have recently garnered attention as a method to reduce the power consumption of neural network inference. A promising category of accelerators utilizes nonvolatile memory arrays to both store weights and perform $\textit{in situ}$ analog computation inside the array. While prior work has explored the design space of analog accelerators to optimize performance and energy efficiency, there is seldom a rigorous evaluation of the accuracy of these accelerators. This work shows how architectural design decisions, particularly in mapping neural network parameters to analog memory cells, influence inference accuracy. When evaluated using ResNet50 on ImageNet, the resilience of the system to analog non-idealities - cell programming errors, analog-to-digital converter resolution, and array parasitic resistances - all improve when analog quantities in the hardware are made proportional to the weights in the network. Moreover, contrary to the assumptions of prior work, nearly equivalent resilience to cell imprecision can be achieved by fully storing weights as analog quantities, rather than spreading weight bits across multiple devices, often referred to as bit slicing. By exploiting proportionality, analog system designers have the freedom to match the precision of the hardware to the needs of the algorithm, rather than attempting to guarantee the same level of precision in the intermediate results as an equivalent digital accelerator. This ultimately results in an analog accelerator that is more accurate, more robust to analog errors, and more energy-efficient.

📄 Content

특수화된 가속기는 최근 신경망 추론의 전력 소비를 줄이는 방법으로 큰 관심을 받고 있습니다. 특히 유망한 가속기 종류는 비휘발성 메모리 배열을 활용하여 가중치를 저장하고, 배열 내부에서 in situ(현장) 아날로그 연산을 수행합니다. 기존 연구들은 성능과 에너지 효율성을 최적화하기 위해 아날로그 가속기의 설계 공간을 탐색했지만, 이러한 가속기의 정확도에 대한 엄밀한 평가가 거의 이루어지지 않았습니다.

본 연구는 아키텍처 설계 결정, 특히 신경망 파라미터를 아날로그 메모리 셀에 매핑하는 방식이 추론 정확도에 어떻게 영향을 미치는지를 보여줍니다. ResNet‑50을 ImageNet 데이터셋에 적용하여 평가한 결과, 시스템이 아날로그 비이상성(셀 프로그래밍 오류, 아날로그‑디지털 변환기(ADC) 해상도, 배열 기생 저항 등)에 대해 보이는 복원력은 하드웨어 내 아날로그 양이 네트워크 가중치와 비례하도록 설계될 때 모두 향상됩니다.

또한, 기존 연구에서 가정하고 있던 바와 달리, 가중치를 여러 디바이스에 걸쳐 비트 슬라이스(bit‑slicing) 방식으로 분산시키는 대신, 가중치를 완전히 아날로그 양으로 저장하면 셀의 불정밀성에 대한 복원력이 거의 동일하게 달성될 수 있음을 확인했습니다. 즉, 가중치를 아날로그 형태로 그대로 유지함으로써, 별도의 비트 분할 없이도 셀 오차에 강인한 특성을 얻을 수 있다는 것입니다.

이러한 **비례성(proportionality)**을 활용하면, 아날로그 시스템 설계자는 하드웨어의 정밀도를 알고리즘이 요구하는 수준에 맞추어 자유롭게 조정할 수 있습니다. 이는 기존 디지털 가속기와 동일한 수준의 중간 결과 정밀도를 보장하려는 시도와는 달리, 알고리즘의 필요에 따라 정밀도를 최적화하는 접근법을 의미합니다. 결과적으로, 이러한 설계 철학은 다음과 같은 세 가지 주요 이점을 제공합니다.

- 정확도 향상: 가중치와 하드웨어 아날로그 값이 비례하도록 설계함으로써, 셀 프로그래밍 오류나 ADC 해상도 제한 등으로 인한 오차가 직접적인 가중치 변형으로 이어지는 것을 최소화합니다.

- 아날로그 오류에 대한 강인성 강화: 비례 관계가 유지되면, 배열 내부의 기생 저항이나 온도 변동 등 환경적 요인에 의해 발생하는 전압/전류 변동이 가중치 스케일에 맞춰 자동 보정되는 효과가 있어, 전체 시스템의 오류 복원력이 크게 증가합니다.

- 에너지 효율성 증대: 가중치를 디지털 형태로 변환하거나 다중 셀에 분산시켜야 하는 추가 연산·전송 비용이 사라지므로, 메모리 접근 횟수와 데이터 이동에 소모되는 에너지를 크게 절감할 수 있습니다.

요약하면, 본 연구는 아날로그 가속기의 설계 단계에서 가중치와 하드웨어 양을 직접적으로 연결시키는 비례 설계가 기존 디지털 대비 동일하거나 더 높은 정확도와 복원력을 제공함과 동시에 전력 소모를 감소시킨다는 중요한 통찰을 제공합니다. 이러한 접근법은 차세대 저전력 인공지능 하드웨어 구현에 있어, ‘정밀도와 에너지 효율 사이의 트레이드오프’를 새로운 방식으로 재조정할 수 있는 가능성을 열어줍니다.

핵심 메시지

- 아날로그 메모리 셀에 가중치를 비례적으로 매핑하면, 셀 오류·ADC 해상도·기생 저항 등 다양한 비이상성에 대한 시스템 복원력이 동시에 향상된다.

- 가중치를 완전한 아날로그 양으로 저장하는 것이 비트 슬라이스 방식보다 동일한 수준의 오류 내성을 제공한다.

- 설계자는 하드웨어 정밀도를 알고리즘 요구에 맞게 유연하게 조정할 수 있어, 디지털 가속기와 동일한 중간 결과 정밀도를 강제할 필요가 없으며, 이는 궁극적으로 정확도·강인성·에너지 효율을 모두 개선한다.

이와 같은 결과는 앞으로 비휘발성 메모리 기반 아날로그 가속기를 설계할 때, ‘가중치‑하드웨어 비례 설계’를 기본 원칙으로 채택함으로써, 보다 실용적이고 경쟁력 있는 인공지능 하드웨어 플랫폼을 구축할 수 있음을 시사합니다.