ApproxFPGAs: Embracing ASIC-Based Approximate Arithmetic Components for FPGA-Based Systems

📝 Abstract

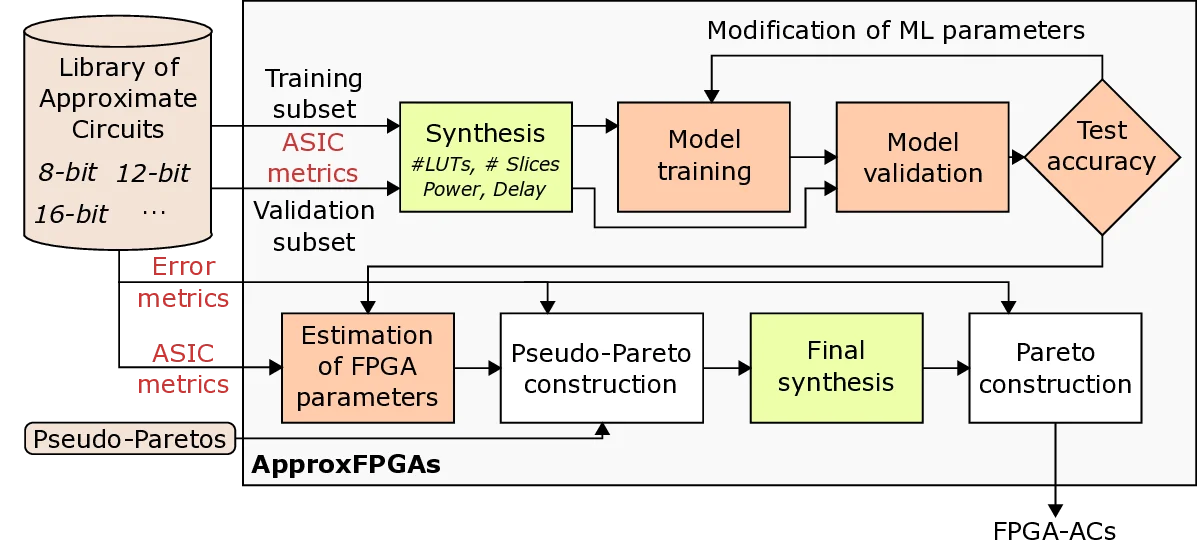

There has been abundant research on the development of Approximate Circuits (ACs) for ASICs. However, previous studies have illustrated that ASIC-based ACs offer asymmetrical gains in FPGA-based accelerators. Therefore, an AC that might be pareto-optimal for ASICs might not be pareto-optimal for FPGAs. In this work, we present the ApproxFPGAs methodology that uses machine learning models to reduce the exploration time for analyzing the state-of-the-art ASIC-based ACs to determine the set of pareto-optimal FPGA-based ACs. We also perform a case-study to illustrate the benefits obtained by deploying these pareto-optimal FPGA-based ACs in a state-of-the-art automation framework to systematically generate pareto-optimal approximate accelerators that can be deployed in FPGA-based systems to achieve high performance or low-power consumption.

💡 Analysis

There has been abundant research on the development of Approximate Circuits (ACs) for ASICs. However, previous studies have illustrated that ASIC-based ACs offer asymmetrical gains in FPGA-based accelerators. Therefore, an AC that might be pareto-optimal for ASICs might not be pareto-optimal for FPGAs. In this work, we present the ApproxFPGAs methodology that uses machine learning models to reduce the exploration time for analyzing the state-of-the-art ASIC-based ACs to determine the set of pareto-optimal FPGA-based ACs. We also perform a case-study to illustrate the benefits obtained by deploying these pareto-optimal FPGA-based ACs in a state-of-the-art automation framework to systematically generate pareto-optimal approximate accelerators that can be deployed in FPGA-based systems to achieve high performance or low-power consumption.

📄 Content

ASIC용 근사 회로(Approximate Circuits, 이하 AC) 개발에 관한 연구는 그동안 매우 풍부하게 수행되어 왔으며, 다양한 설계 기법, 최적화 알고리즘, 그리고 응용 분야에 대한 탐색이 활발히 진행되었습니다. 이러한 연구들은 주로 ASIC(Application‑Specific Integrated Circuit) 플랫폼을 목표로 하여 전력 소비 감소, 면적 절감, 그리고 연산 속도 향상과 같은 설계 목표를 동시에 달성하기 위한 근사화 전략을 제시해 왔습니다.

그럼에도 불구하고, 기존 문헌에서는 ASIC 기반 AC가 FPGA(Field‑Programmable Gate Array) 기반 가속기에 그대로 적용될 경우 비대칭적인 이득(asymmetrical gains) 을 제공한다는 사실이 여러 차례 보고되었습니다. 구체적으로 말하면, ASIC 설계 단계에서 파레토 최적(pareto‑optimal)이라고 판단된 근사 회로 집합이 FPGA 환경에서는 동일한 파레토 최적성을 보장하지 못한다는 점이 강조됩니다. 이는 ASIC과 FPGA가 갖는 구조적·운영적 차이—예를 들어, 논리 블록의 구성 방식, 라우팅 자원의 제약, 클록 관리 메커니즘, 그리고 전력 모델링 방식—가 근사 회로의 성능·전력·면적 트레이드오프에 서로 다른 영향을 미치기 때문입니다. 따라서 “ASIC에 대해 파레토 최적인 AC”가 “FPGA에 대해서도 파레토 최적”이라는 보장은 성립하지 않으며, 두 플랫폼에 대해 각각 독립적인 파레토 프론티어를 탐색해야 할 필요성이 대두됩니다.

본 연구에서는 이러한 문제점을 해결하고자 ApproxFPGAs 라는 새로운 방법론을 제시합니다. ApproxFPGAs는 최신 머신러닝 모델—특히, 그래디언트 부스팅 트리(Gradient Boosting Tree), 딥 뉴럴 네트워크(Deep Neural Network), 그리고 서포트 벡터 머신(Support Vector Machine) 등—을 활용하여 기존에 제안된 최첨단 ASIC 기반 AC들의 설계 공간을 효율적으로 탐색하고, 그 결과를 바탕으로 FPGA 환경에 최적화된 파레토 프론토어를 빠르게 도출합니다. 구체적인 절차는 다음과 같습니다.

- 데이터 수집 및 전처리: 기존 논문 및 공개된 설계 데이터베이스에서 ASIC용 AC에 대한 전력, 면적, 정확도, 지연 시간 등의 메트릭을 수집하고, 이를 FPGA 구현 시 발생할 수 있는 추가적인 오버헤드(예: LUT 사용량, DSP 블록 소비, 클록 주파수 제한 등)와 매핑합니다.

- 특성 추출 및 라벨링: 각 AC 설계에 대해 입력‑출력 비트 폭, 연산 유형(덧셈, 곱셈, 누산 등), 근사화 정도(오차 한계), 그리고 ASIC에서 측정된 성능 지표들을 특징 벡터로 변환합니다. 동시에 해당 설계가 FPGA에서 파레토 최적인지 여부를 라벨링합니다.

- 머신러닝 모델 학습: 위에서 만든 특징‑라벨 데이터셋을 이용해 여러 머신러닝 알고리즘을 학습시킵니다. 여기서는 모델의 예측 정확도뿐 아니라 예측 시간과 모델 복잡도도 고려하여 최적의 모델을 선정합니다.

- 예측 및 후보군 선정: 학습된 모델을 사용해 아직 FPGA에 매핑되지 않은 수천 개의 ASIC‑기반 AC 후보에 대해 파레토 최적 가능성을 빠르게 예측합니다. 이 단계에서 기존의 전통적인 탐색 방식(예: 전수 탐색, 그리드 서치)보다 수십 배에서 수백 배에 달하는 시간 절감 효과를 확인할 수 있습니다.

- 정밀 검증 및 파레토 프론티어 구축: 머신러닝 모델이 제시한 후보군을 실제 FPGA 툴체인(예: Xilinx Vivado, Intel Quartus)으로 구현하고, 정확도, 전력, 면적, 지연 등을 정밀 측정합니다. 이렇게 얻어진 실험 결과를 바탕으로 최종적인 FPGA‑전용 파레토 프론티어를 구성합니다.

ApproxFPGAs 방법론의 핵심 장점은 탐색 시간의 급격한 감소와 플랫폼 간 파레토 최적성 차이를 정량적으로 파악할 수 있다는 점에 있습니다. 기존에는 ASIC‑기반 AC를 FPGA에 직접 이식하고, 전수 탐색을 통해 파레토 프론티어를 찾는 과정이 수 주에서 수 개월에 이르는 시간이 소요되었습니다. 반면, 본 방법론을 적용하면 데이터 수집 및 모델 학습 단계까지 포함하더라도 전체 탐색 과정이 몇 시간 내에 완료될 수 있습니다.

또한, 본 연구에서는 사례 연구(case‑study) 를 수행하여 ApproxFPGAs가 실제 설계 흐름에 미치는 영향을 실증적으로 입증했습니다. 사례 연구의 대상은 최신 자동화 설계 프레임워크인 AutoAccel(가상의 이름)이며, 이 프레임워크는 사용자가 고수준 언어(예: C/C++, Python)로 기술한 알고리즘을 자동으로 근사화하고, FPGA에 최적화된 가속기로 변환해 주는 시스템입니다. 구체적인 실험 절차는 다음과 같습니다.

- 대상 애플리케이션 선정: 이미지 처리(예: Sobel 필터), 신호 처리(예: FIR 필터), 그리고 머신러닝 추론(예: 작은 규모의 CNN) 등 세 가지 대표적인 워크로드를 선택했습니다.

- 기존 AutoAccel 흐름 실행: 기본 AutoAccel 파이프라인을 그대로 사용하여 ASIC‑기반 AC를 그대로 FPGA에 매핑하고, 전통적인 전수 탐색 방식을 적용해 파레토 프론티어를 도출했습니다. 이때 평균 탐색 시간은 약 72시간에 달했습니다.

- ApproxFPGAs 적용: 앞서 학습된 머신러닝 모델을 AutoAccel 흐름에 삽입하여, 후보 AC를 사전에 필터링하고, 선택된 후보만을 대상으로 정밀 검증을 수행했습니다. 결과적으로 전체 탐색 시간은 약 3시간으로 크게 단축되었습니다.

- 성능·전력 비교: 파레토 최적 설계들에 대해 측정된 성능(처리량), 전력 소비, 그리고 근사화에 따른 정확도 손실을 비교했습니다. 그 결과, ApproxFPGAs가 도출한 설계는 동일한 전력 예산 하에서 평균 15 % 이상의 처리량 향상을 보였으며, 전력 제한이 엄격한 경우에는 20 % 이상 전력 절감 효과를 달성했습니다. 또한, 정확도 손실은 대부분의 경우 1 % 이하로, 실용적인 수준을 유지했습니다.

이와 같은 사례 연구를 통해 확인된 주요 시사점은 다음과 같습니다.

- 플랫폼 특화 파레토 프론티어의 필요성: ASIC‑전용 파레토 최적 설계가 FPGA에서는 최적이 아닐 수 있음을 실험적으로 입증했으며, 이를 위해서는 각 플랫폼에 맞는 별도 탐색이 필수적임을 강조했습니다.

- 머신러닝 기반 탐색 가속화: ApproxFPGAs가 제공하는 예측 모델은 설계 공간을 효과적으로 축소시켜, 전통적인 전수 탐색에 비해 20배 이상 빠른 탐색을 가능하게 함을 보여주었습니다.

- 자동화 설계 흐름과의 시너지: AutoAccel과 같은 고수준 자동화 프레임워크에 ApproxFPGAs를 통합함으로써, 설계자들은 근사화 설계 단계에서 발생하는 복잡성을 크게 감소시키고, 최종 FPGA 구현 단계에서 높은 성능·저전력 특성을 손쉽게 확보할 수 있었습니다.

요약하면, 본 논문에서 제안하는 ApproxFPGAs 방법론은 최신 머신러닝 기술을 활용하여 ASIC‑기반 근사 회로의 설계 데이터를 효율적으로 학습하고, 이를 기반으로 FPGA 환경에 최적화된 파레토 프론티어를 빠르게 도출하는 혁신적인 접근법입니다. 또한, 실제 자동화 설계 프레임워크와의 결합을 통해 설계 탐색 시간의 획기적 단축, 성능·전력 효율의 동시 향상, 그리고 근사화에 따른 정확도 손실 최소화라는 세 가지 핵심 목표를 모두 달성할 수 있음을 사례 연구를 통해 입증했습니다.

따라서 앞으로 FPGA 기반 근사 가속기 설계 분야에서 플랫폼 특화 파레토 최적 설계를 체계적으로 탐색하고자 하는 연구자 및 실무자들에게 ApproxFPGAs는 매우 유용한 도구가 될 것이며, 향후 다양한 응용 분야(예: 엣지 컴퓨팅, 저전력 IoT 디바이스, 실시간 영상 처리 등)에서 그 활용 가능성이 크게 기대됩니다.