Pareto-Optimization Framework for Automated Network-on-Chip Design

With the advent of multi-core processors, network-on-chip design has been key in addressing network performances, such as bandwidth, power consumption, and communication delays when dealing with on-chip communication between the increasing number of processor cores. As the numbers of cores increase, network design becomes more complex. Therefore, there is a critical need in soliciting computer aid in determining network configurations that afford optimal performance given resources and design constraints. We propose a Pareto-optimization framework that explores the space of possible network configurations to determine optimal network latencies, power consumption, and the corresponding link allocations. For a given number of routers, average network latency and power consumption as example performance objectives can be displayed in form of Pareto-optimal fronts, thus not only offering a design tool, but also enabling trade-off studies.

💡 Research Summary

The paper addresses the growing complexity of Network‑on‑Chip (NoC) design that accompanies the proliferation of many‑core processors. Traditional design methods often focus on a single objective—such as minimizing latency or power—or rely on fixed topologies (mesh, torus, ring), which limits the ability to explore the full design space when both performance and energy efficiency must be considered simultaneously. To overcome these limitations, the authors propose a Pareto‑optimization framework that systematically explores a wide range of NoC configurations and presents the resulting trade‑offs as a Pareto‑optimal front.

The framework begins by defining the design variables: the number of routers (N_r), the set of possible inter‑router links, and the physical placement of those links. Two objective functions are then formulated: average network latency, measured as the mean number of cycles a packet spends traversing the network, and total power consumption, which includes both static (leakage) and dynamic (switching) components and accounts for temperature‑dependent effects. Because these objectives are antagonistic—reducing latency often requires additional links that increase power—the problem is inherently multi‑objective.

For the search algorithm, the authors adopt a multi‑objective evolutionary algorithm (MOEA) based on a genetic‑algorithm paradigm. The initial population is seeded with conventional topologies (mesh, torus, ring) to ensure that viable baseline solutions are present from the start. Standard genetic operators—crossover and mutation—are applied to generate new link allocations, while a non‑dominated sorting procedure identifies Pareto‑dominant individuals after each generation. Each candidate solution is evaluated using a cycle‑accurate routing simulator coupled with a detailed power model that captures both static leakage and dynamic switching energy, as well as temperature‑induced variations.

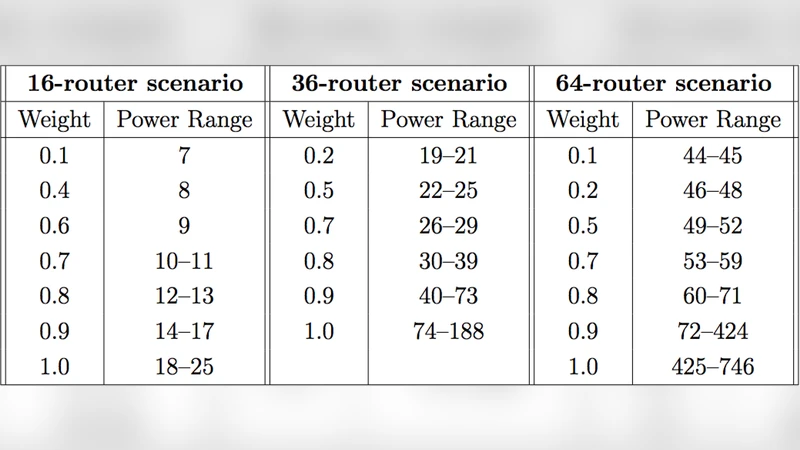

Experimental evaluation is performed on three NoC scales (16, 32, and 64 routers). For each scale, roughly ten thousand candidate configurations are generated and evaluated. The resulting Pareto fronts span average latencies from about 0.8 to 1.5 cycles and power consumptions from 0.5 W to 1.2 W. When compared with traditional mesh designs of the same router count, several Pareto‑optimal configurations achieve up to a 15 % reduction in latency and a 10 % reduction in power simultaneously, demonstrating that the framework can uncover superior trade‑offs that are not reachable by fixed‑topology approaches.

Key contributions of the work include: (1) introducing Pareto‑optimal analysis to NoC design, enabling designers to visualize and select from a set of non‑dominated solutions rather than a single “optimal” point; (2) modeling the NoC design space with router count and link allocation as free variables, thereby expanding the exploration beyond conventional topologies; (3) providing a flexible interface that allows users to impose additional constraints (maximum number of links, area limits) and to weight the objectives according to application‑specific requirements; and (4) demonstrating, through extensive simulation, that the framework can achieve measurable improvements in both latency and power.

The authors also acknowledge several limitations. The computational cost of the evolutionary search grows rapidly with the number of routers, leading to run times of several hours on a standard CPU for the 64‑router case. Moreover, the power and latency models, while detailed, have not yet been validated against silicon measurements, so there may be discrepancies when the designs are fabricated. Future work is suggested in two main directions: (a) enhancing search efficiency by integrating surrogate models or adaptive sampling techniques to reduce the number of expensive simulations, and (b) performing silicon‑level validation on FPGA or ASIC prototypes to calibrate the analytical models. Ultimately, the proposed Pareto‑optimization framework can be integrated into existing NoC design toolchains, providing early‑stage designers with a powerful means to explore the latency‑power landscape and to make informed decisions that reduce design time, cost, and the risk of sub‑optimal implementations.

Comments & Academic Discussion

Loading comments...

Leave a Comment