An Improved Majority-Logic Decoder Offering Massively Parallel Decoding for Real-Time Control in Embedded Systems

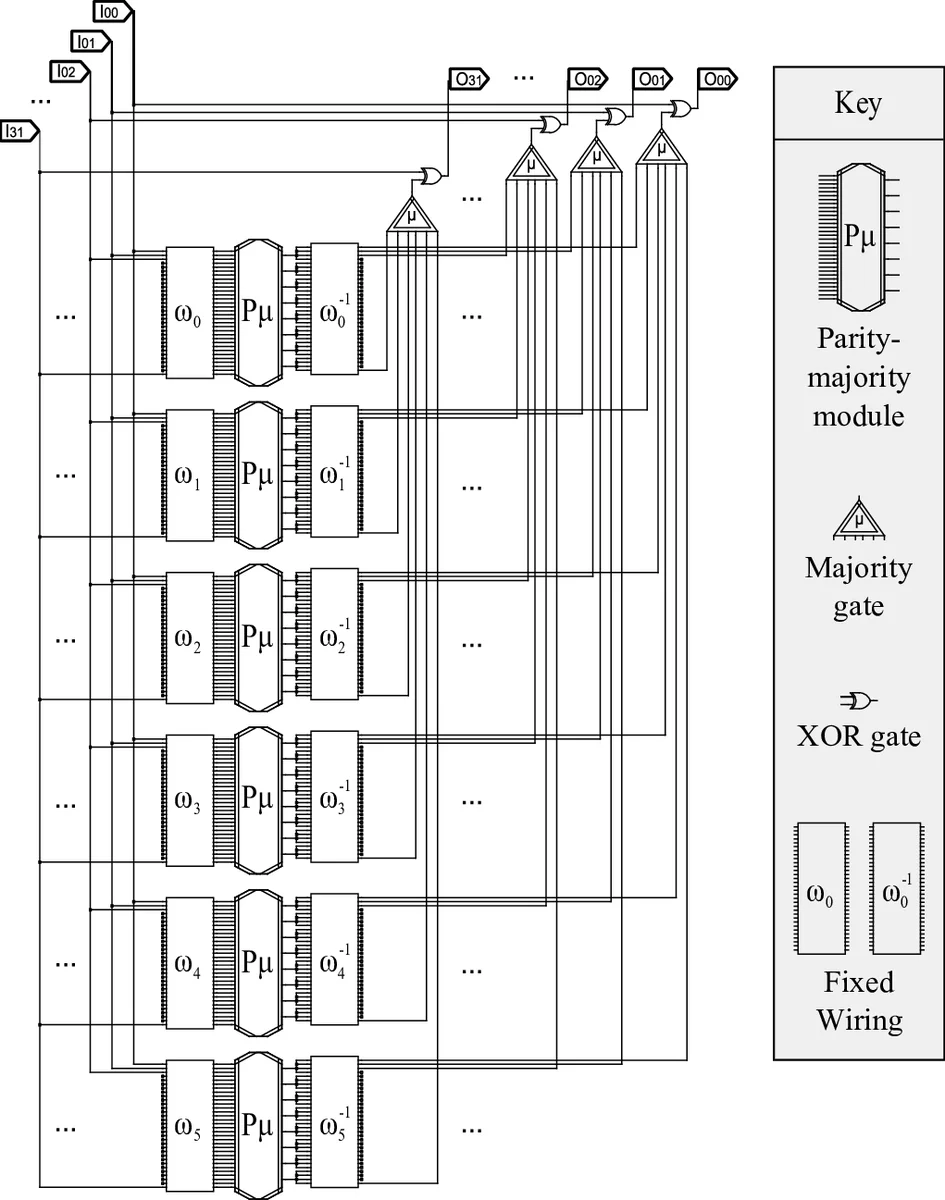

We propose an easy-to-implement hard-decision majority-logic decoding algorithm for Reed-Muller codes RM(r,m) with m >= 3, m/2 >= r >= 1. The presented algorithm outperforms the best known majority-logic decoding algorithms and offers highly parallel decoding. The result is of special importance for safety- and time-critical applications in embedded systems. A simple combinational circuit can perform the proposed decoding. In particular, we show how our decoder for the three-error-correcting code RM(2,5) of dimension 16 and length 32 can be realized on hardware level.

💡 Research Summary

This paper presents a novel hard-decision majority-logic decoding algorithm for Reed-Muller codes RM(r, m), where m ≥ 3 and m/2 ≥ r ≥ 1. The primary objective is to enable massively parallel decoding with constant parallel time, a critical requirement for safety- and time-critical real-time control applications in embedded systems, such as automotive driver assistance or medical devices.

The authors begin by revisiting Chen’s well-known two-step majority-logic decoding algorithm. Chen’s algorithm operates on an admissible set of flats of dimensions 0, r, and r+1. It involves four functional levels: computing check-sums for (r+1)-flats, performing majority votes to determine the state of r-flats, another majority vote to determine single-bit errors, and a final XOR to correct the received word. While enabling two-step decoding, its complexity is O(nδ²) function calls, where n=2^m is the code length and δ=2^(m-r) is the minimum distance.

The core contribution of this work is a significantly improved algorithm that reduces this complexity. The key innovation lies in using only a specially constructed set F of r-flats, completely eliminating the need for (r+1)-flats during the decoding process. This set F is constructed based on (δ-2) pairwise trivially intersecting r-dimensional subspaces U_l and their complementary subspaces W_l. The resulting set of δ(δ-2) r-flats has two crucial properties: any two distinct r-flats intersect in at most one point, and every point in the space Z₂^m is contained in exactly (δ-2) of these r-flats.

Leveraging this structure, the authors establish a new decoding theorem. The error status of a specific r-flat (whether it contains an odd number of errors) is determined not by checking super-sets like (r+1)-flats, but by comparing its own check-sum (ς_l,i) with the majority result (μ_l) computed over all δ r-flats derived from the same subspace U_l. If they differ, the r-flat is odd. This elegant insight drastically simplifies the second decoding step. The complete algorithm thus consists of only three parallelizable stages: 1) Compute the check-sums ς_l,i for all r-flats in F. 2) For each group of r-flats sharing a common U_l, compute a single majority value μ_l. 3) For each bit position, apply majority logic over the (δ-2) r-flats containing it to determine the error bit η_i.

The complexity analysis confirms a major improvement: the number of parallel function calls is reduced from O(nδ²) to O(nδ). More importantly, all operations within each step are independent and can be executed concurrently, guaranteeing decoding in constant parallel time. This makes the algorithm exceptionally suitable for hardware implementation using simple combinational logic, without sequential elements. The paper provides a concrete example of how the decoder for the RM(2,5) code (length 32, dimension 16, correcting 3 errors) can be realized at the hardware level.

In conclusion, this work offers an easy-to-implement, highly parallel, and less complex majority-logic decoder for a broad class of Reed-Muller codes. It effectively bridges the gap between the algebraic robustness of RM codes and the stringent latency requirements of modern real-time embedded systems, presenting a practical solution for forward error correction in safety-critical applications.

Comments & Academic Discussion

Loading comments...

Leave a Comment