A low power DAQ system with high-speed storage for submersible buoy

Submersible Buoy (SB) is an important apparatus capable of long-term, fixed-point, continuous and multi-directional measurement of acoustic signals and hydrological environment monitoring in the harsh marine environment, providing important informati…

Authors: Zhilei Zhang, Peng Miao, Houbing Liu

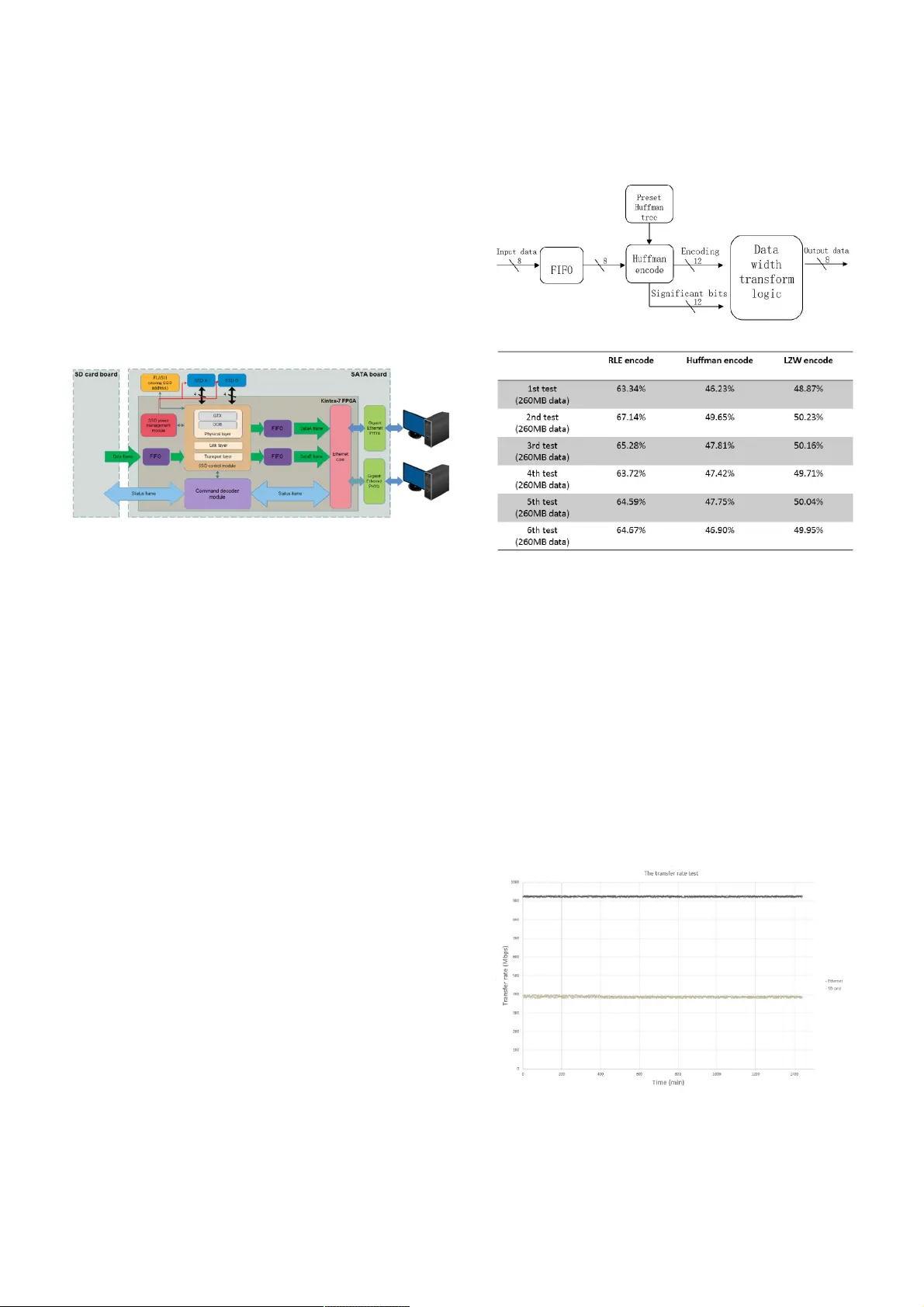

A low powe r DAQ s y ste m w ith hi g h -spe ed storag e for sub mersib le buo y Zhi lei Zhang, Peng Miao, Houbing Li u , K un Hu, Fe ng Li, Ge Jin A bst ract– Submers i b le Buo y (SB) is a n import an t appa r a t us c apable of long-te rm, f ix e d - point, c on tin uous and m u l ti-dir ectional meas ure ment of aco u st ic signals and h y d r o l og i cal e n vir onment monit o ri ng in t he harsh m arine envir o nme n t , providi ng i mportant infor matio n f o r h y d r o l ogical e n v ironme n t re s earc h , marine org anism r esearc h and pr o t ec tion . We will d e scri be a r eal-time dat a acq u i siti o n (DA Q ) syste m with multiple d e sign s to mee t lo w- power c onsumptio n and h ig h-spee d dat a t ransmi ssi on . I. I NTRO DUCTION he SB has long runtim e s and reco v ery c y cles, a nd the entire s y stem is po w ered b y batte r ie s . So, the DAQ sy s tem shoul d be as low -po wer as p oss ib l e due to the requirem ent of lo n g- t erm, sta b le u nde rwater operation. Meanwhile , the DA Q sy stem al so demands lar ge capacity storage b ecaus e o f long runtime a nd relatively h ig h sam p l ing r ate. O wi n g to the wi de dist r ibutio n o f the SB, t h e DAQ sy stem must e nsure h i g h- speed data stora ge a s well as high-speed upload path to the host when retrie v ing data in order to reduce data coll e ction t ime and i mprove t he extracti on effic iency. To dea l with such sit uations, we d esign a data a cqu i si t ion sy stem, which cons is t s o f multi-cha nnel A DC s for hy drop hone s s ig nal digitizat ion; Sp arta n -6 FP G A f o r da t a packa ge, ca p t u re an d com p ress ion; SD car d for short-term dat a storage; SSD f or long-term d at a stora g e along with du a l Gig abit Ethernet for d ata upload . P relimi nar y t est show s that t he DAQ sys tem c a n achieve high-s p e ed data conve rs i o n, stora ge an d readou t at comparati v ely lo w-p ow er. II. S YSTEM D ESIGN Throug h anal y zing t he s y s t e m requ i rem e nts, characteris ti c s a nd f easibili t y of the SB , this p a per d e sc ribes the architect ure of the DA Q s y s te m: the Front-End board (FEB) f o r data a cqu i si t ion and packa ging; the SD car d bo a rd f or d ata c ompressi on a nd short-term data storage; the S ATA bo a rd for l ong-ter m data st orage and hig h -spee d upload ing. Manuscript r ece i ved J une 23, 2018. This work was suppo r ted by the N a ti onal Natural S c i ence Foundation of Chi n a un d er Gra nts 1146 1141010 and 11 3 7517 9 , and in part by " the Fundamental R esearch Funds fo r the Centr a l Universi ties" u nder grant No. WK23 6000 0 005. Zhilei Z h an g, Peng Mi a o , Houbi ng Li u, K u n Hu, F eng Li, and G e J in are w ith State Key Laboratory of P a rticl e Det ection and E l e ct r o n i cs , University of Science and T e ch nology of Chi n a, H efei, Anhui 23 0 0 26, P.R. of C h ina ( phone: + 8 6-551-6360 6 4 95, e-mail: zzlei@mail.u stc.edu.cn, mpmp@mail. us t c.edu.cn, l u hb@mail . u stc.edu.c n, khu@. us t c.edu.cn, p h o n el ee@ustc . ed u . cn, g o ldjin@ustc. edu. c n ) A. Front End boa r d The sc h em a t i c str ucture of the FEB i s s hown in F ig. 1. The core of the FEB c onsists of a Sp a rtan-6 F P GA a nd eight h y drop hon es with 5~10K sam p l ing r ates . The wat c h ci r cuit im mediately sends a trigger signal to the FEB when moni tori ng the signal o f inte rest, and the FEB starts to collect and p ack age the da t a o f each h y drop hone and ot her s ensors. Each p a cket c o m po s es a data frame afte r adding p a cket number, header of f rame, end of f r ame and CRC16 che ck d igit . Fi nall y FEB sends data frame to t he SD ca rd bo a rd t h rough the s erial port. Fi g .1. Schemati c B lock dia g ra m of the F ront-E n d b oa r d B. S D c a r d bo a r d The schema t ic block dia gr am of the S D ca rd board is ill ustrated in F i g . 2. The SD card board comp res se s t h e frame data which is recei ved from the FEB and write to SD card . FPGA cont rol tw o SD car ds based on ping-pong opera tion to p rev ent data loss. Meanwhile , either SD c ard which i s not working is comple te shut d ow n b y FPGA. When a SD card reac h es stora g e th reshol d , the S ATA board will be p owere d - on in the next data acq ui sitio n. SD mode is used t o write SD ca rd at 10 MB/s f or low-p ow er cons umption and UHS m ode is used to read SD car d data at 90 MB/ s f or high-s p eed tra nsmis s io n with SATA b oard. Fi g .2. Schemati c block diagra m of t h e SD c a r d bo a r d T C. SATA board The sche m atic b lo ck diagr am o f th e SATA c ard board is i llustrated in Fig. 3 . T he S ATA bo a rd receive th e f r a m e d ata f rom the SD card board and w rit e to 1T B SSD. I n order t o red uce p ower consumpti on, FP GA will power-off either SS D whi ch is not at w ork. When the h ost r e q uir es data retrieve, all dat a in the SD car ds is forcibly tr ansf erred to the SSD . Th e n t he hos t read out all data from S SD through the d ua l Gigab it Ether net. D e spite th e high p ower consu mp ti o n o f t h e SATA bo a rd, it runs onl y 0 .3% of the t o t al s y s tem t i me and do es not aff ect the design goal of low-powe r. Fig.3. Sche m atic bl ock diagram o f t he SATA boar d III . L OW - POWER D ESIGN A. D e vi ce Selecti o n Use S partan -6 FP G A f o r lo w-p ow er co nsumption . (Sparta n-6 FPGA c an n ot meet the re q uir ements of SATA bo a rds. The Kintex -7 FP G A is chosen for h igh powe r c onsumption, but the running t ime of t he SATA board is abo ut 0.3% of the Front -End/SD car d board, whi c h does not aff ect t he desi g n of t h e low- p ower .) B. Power Ma nageme n t The F EB is p ower ed on by the wat ch circuit only when a t arget of i nterest is f ound and normal l y p ow ered o ff to r educe po w er c o nsu mption. A f ter the initiali z at ion o f FEB, t he SD c ard board is po we red on b y the FEB. In ad di t ion, the SD card bo a rd usually works in the ping-pong mode and the F PG A wil l complete ly s hut down t h e idle SD ca rd . The SATA boa rd i s powered on only whe n the SD ca rd bo a rd reac hes the t hreshol d or the host comp ut er nee d s to ex tract data . The idle SSD will b e powered off b y the FPGA on SATA bo a rd when t he SATA board i s operating prop e rly . All dig ital parts o f har dware a re po we red b y DC / D C t o redu ce p ow er c onsumption. C. Lossles s d ata co mp r essio n Curre ntly the los s l ess da ta c o mpress ion encode b ase d on FPGA a re mainly RL E en code, H uffman encode, a nd LZW e ncode. By c omp arin g the 1.5GB act ual measure d data fr om Qingda o La k e w hich used diff erent los s le s s com p res sion e ncode (shown in Fig . 5.), the comp res sion efficiency o f RLE e ncode i s too low. T he co mpression eff i ci enc y of LZW e ncode i s a bit l ower than Huffman e ncode. In general, Huff man c od ing is eas y to accom plish, and t he a ddition of po w er c o nsu mption i s l e ss t han 10mW. Using lo ssle s s data c ompressi on greatly i ncreases the eff e c t ive data tra nsmissio n speed , red uces s y s tem operating t ime, and dec r e ases p ow er c onsumption i n disguise. [2 ][3] Fig.4. Sche m atic b l ock diagram of lossless dat a c om pr ession Fi g . 5. Dat a com p ression compar ison IV. E XPERIMENTAL R ES U LTS A. H i g h-s p e ed tr an s missio n Test In FEB FPGA, all o f inp ut s are rep l aced with c o ntr ollable linea r-growth coun ters to c omplete data t r ansf er p roce sses. The received d ata and the tr a n s mission time of every 2 048 data f r ame s are monitore d on the S D card bo a rd and the S A TA b oa rd. Our tests show that the F EB gene rates total o f 8*107 b y t e s, and the d ata received on the SD ca rd bo a rd a n d the S ATA b oa rd kee p s inc re asi ng l inearl y . I n o the r words, there are no errors in the transm ission. The a v e rage speed o f the SD card b oar d and SATA bo a rd i s shown in Fig. 6 . In addi tion, each data fra me h a s an inde p e nde nt p ack et number, and th e p a cke t nu m ber receive d f ro m S ATA b oard data has al so b e en cont inuous, in d icatin g t hat t he data packet has never b e en l ost. [ 4 ] Fi g . 6. Tr ans fer rate test of SD c ard and gigab it et hernet B. Lo ss les s da t a co mp r essio n The re sult o f lo ssless data compressio n has show n i n Fig. 5 . , whic h use d actual measu red data from Qingdao Lake. It indi cates th a t th e power consumptio n i s redu ce d a half u nde r the same cond it ions, mean while th e e ff ective d ata speed i s dou b l ed a nd the limit o f tran s m issi on sp e ed on h a rdware i s breakthroug h. V. C ONCL U SION This p a p e r real izes large capac it y stora ge and h ig h-speed data transmiss ion through research and applic a ti on o f SD c ard UHS mode, SATA prot ocol and Gigabit . A nalyze and p rac t ice f rom vari ous aspects to reduce s y stem p ow er c onsumption. The prototy p e of t he FEB, the S D car d b oar d (shown i n Fig.7 .), a nd th e SATA b oar d (shown in Fig .8 . ) w a s des i g ned and ver ified f or it s function and per f o r mance . As a resul t , T he DAQ sy s t em satisf ies the re q uire ment of t h e ta rge t . R E F E RENCES [1] Fan Y , “ F PG A-based data acquisition system,” in Signal Processing, Communi cations and Com p uting ( I CSPCC), 2 0 11 IEE E I nternati onal Conferenc e on. IEEE , 2011, pp. 1- 3 . [2] Glas s L, Biran G , Gol ander A. C ompressio n algorit hm incorporati ng dynami c selectio n o f a p r edefined huff m an dictio nary: U.S. P aten t 8,610,6 0 6[P] . 2013-1 2-1 7 . [3] Lek a t sas H, H enkel J , Wol f W. C od e co m p ress io n for low p ower embed d ed s ys t em d es i gn[C]//Pro ceed i ngs o f t he 37t h Annual D es i gn Automati on C onference. ACM, 2000: 2 9 4-299. J V H a t f i e l d, S B ell and P I Ne aves . A w edge and st r ip particle dete c t or bas ed on a current-mod e approach [ J]. C irc u it s & Syst ems , 1995, 1:1 9 3-1 96. [4] L u H, H u K, Wang X, et al . High s p eed ethernet a pplicat i on for t he trigger e lectronic s o f the new small w h eel[C]// Real T i m e C onference (RT), 2 0 1 6 IE E E-N PSS. IEE E, 201 6 : 1-4. Fig.7. pr o tot ype of SD car d board Fig.8. pr o tot ype of SATA bo a r d

Original Paper

Loading high-quality paper...

Comments & Academic Discussion

Loading comments...

Leave a Comment