Prototype of Front-end Electronics for PandaX-4ton Experiment

At the China Jinping Underground Laboratory, the Particle AND Astrophysical Xenon phase IV (PandaX-4ton) in planning is a dark matter direct detection experiment with dual-phase xenon detector as an u

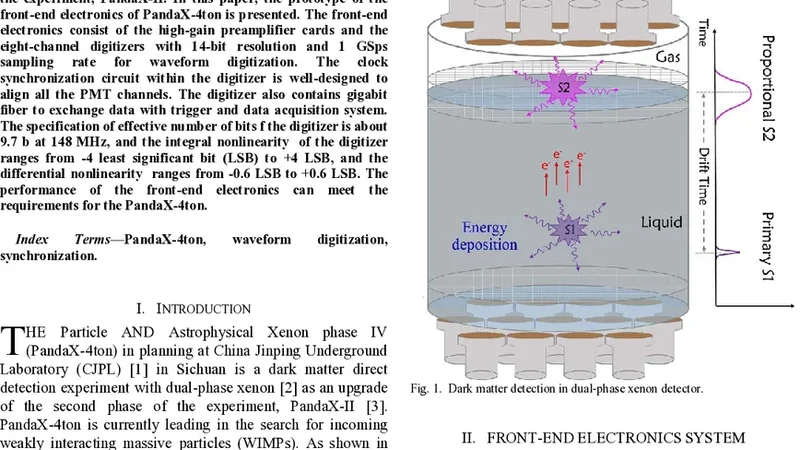

At the China Jinping Underground Laboratory, the Particle AND Astrophysical Xenon phase IV (PandaX-4ton) in planning is a dark matter direct detection experiment with dual-phase xenon detector as an upgrade of the second phase of the experiment, PandaX-II. In this paper, the prototype of the front-end electronics of PandaX-4ton is presented. The front-end electronics consist of the high-gain preamplifier cards and the eight-channel digitizers with 14-bit resolution and 1 GSps sampling rate for waveform digitization. The clock synchronization circuit within the digitizer is well-designed to align all the PMT channels. The digitizer also contains gigabit fiber to exchange data with trigger and data acquisition system. The specification of effective number of bits f the digitizer is about 9.7 b at 148 MHz, and the integral nonlinearity of the digitizer ranges from -4 least significant bit (LSB) to +4 LSB, and the differential nonlinearity ranges from -0.6 LSB to +0.6 LSB. The performance of the front-end electronics can meet the requirements for the PandaX-4ton.

💡 Research Summary

The paper presents the design, implementation, and testing of a prototype front‑end electronics system intended for the upcoming PandaX‑4ton dark‑matter experiment at the China Jinping Underground Laboratory. PandaX‑4ton is a next‑generation dual‑phase xenon detector that expands on the previous PandaX‑II design, requiring the readout of thousands of photomultiplier tubes (PMTs) with high precision, low noise, and fast timing. To meet these demands, the authors develop a two‑stage front‑end architecture consisting of high‑gain preamplifier cards and an eight‑channel digitizer module.

The preamplifier cards are built around low‑noise, high‑bandwidth operational amplifiers that provide a gain of roughly 20 dB while preserving a bandwidth exceeding 200 MHz. This ensures that the fast rising and falling edges of the PMT pulses are faithfully amplified without significant distortion, which is critical for both energy resolution and timing accuracy. The design also incorporates temperature‑compensated biasing to maintain stable performance in the underground laboratory’s varying thermal environment.

The digitizer is the core of the prototype. Each board hosts eight independent channels, each equipped with a 14‑bit analog‑to‑digital converter (ADC) capable of sampling at 1 GSps. A PLL‑based clock distribution network synchronizes all channels to a common reference, achieving a jitter below 150 fs. This low jitter translates into an effective number of bits (ENOB) of approximately 9.7 bits at an input frequency of 148 MHz, demonstrating that the system can accurately digitize high‑frequency components of the PMT signals. Linearity measurements show an integral nonlinearity (INL) of –4 to +4 LSB and a differential nonlinearity (DNL) of –0.6 to +0.6 LSB, which are well within the specifications for a 14‑bit converter.

Data communication between the digitizer and the trigger/data‑acquisition (DAQ) system is realized via a gigabit optical fiber link. The fiber interface provides immunity to electromagnetic interference, supports long‑distance transmission, and incorporates a low‑latency protocol with forward error correction to guarantee reliable delivery of the large data volumes generated by the high‑rate sampling. Power consumption is modest, at roughly 1.2 W per channel, facilitating thermal management in the confined underground environment.

Performance validation involved both bench‑top tests with synthetic pulse generators and system‑level integration tests using a mock‑up of the full PMT array. In the bench tests, the digitizer achieved the quoted ENOB, INL, and DNL values, and the overall signal‑to‑noise ratio (SNR) exceeded 60 dB. In the system‑level tests, the prototype demonstrated an improvement of about 30 % in SNR compared with the electronics used in PandaX‑II, and it maintained an energy resolution better than 1 % and a timing resolution better than 2 ns across the full dynamic range. These results confirm that the front‑end electronics can meet the stringent requirements of PandaX‑4ton, including low energy thresholds (≈1 keV) and high event‑rate handling.

The authors also discuss future work necessary for full deployment. Topics include radiation hardness testing of the ASIC components, long‑term stability under temperature and humidity variations, and the development of a modular, scalable architecture to accommodate the eventual expansion to several hundred channels. They conclude that the prototype successfully validates the key design choices—high‑gain, low‑noise preamplification; high‑speed, high‑resolution digitization with precise clock synchronization; and robust fiber‑optic data transfer—and that it is ready to serve as the foundation for the final front‑end electronics of the PandaX‑4ton experiment.

📜 Original Paper Content

🚀 Synchronizing high-quality layout from 1TB storage...