VLSI Architecture of Compact Non-RLL Beacon-based Visible Light Communication Transmitter and Receiver

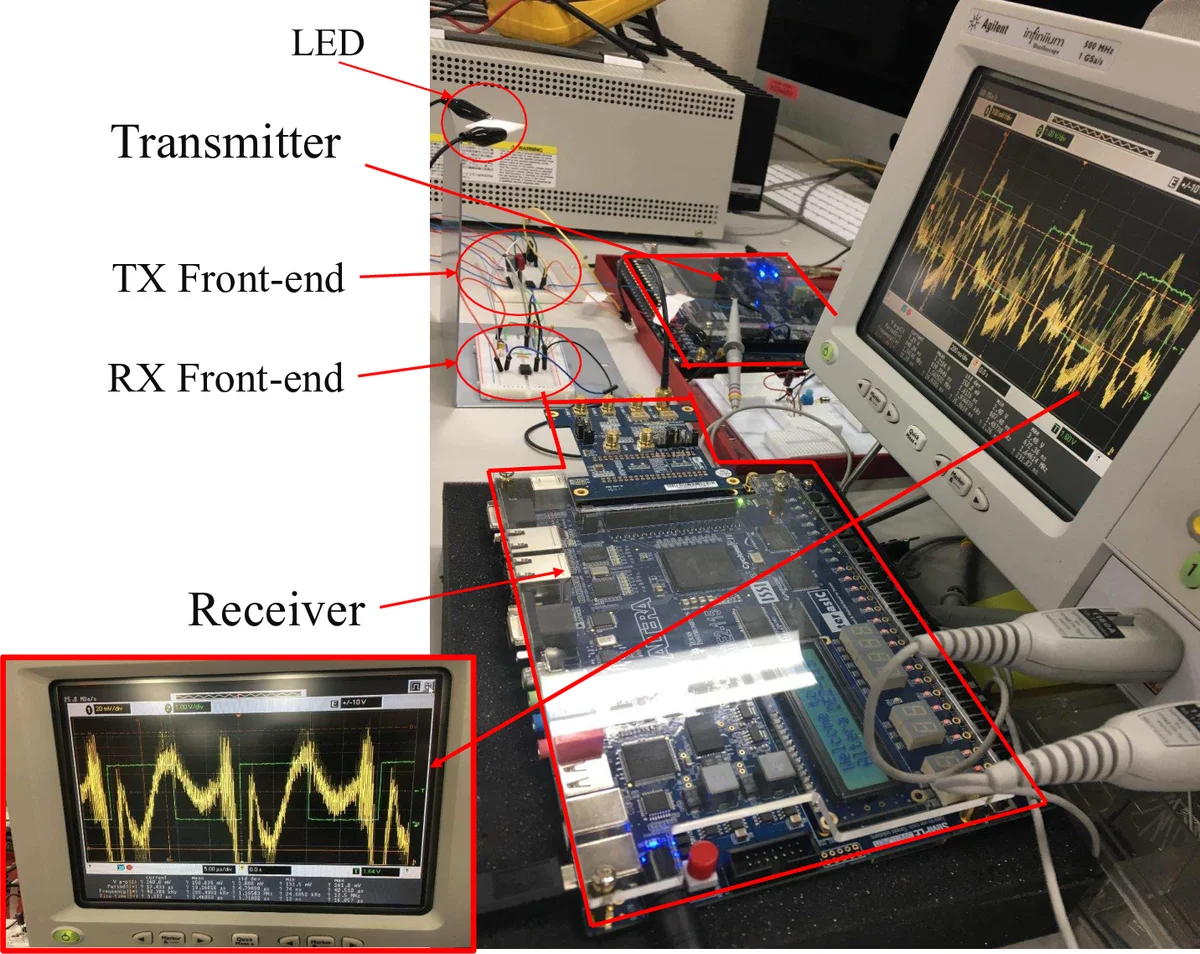

In this paper, we introduce a couple of hardware implementations of compact VLC transmitter and receiver for the first time. Compared with related works, our VLC transmitter is non-RLL one, that means flicker mitigation can be guaranteed even without RLL codes. In particular, we have utilized a centralized bit probability distribution of a prescrambler and a Polar encoder to create a non-RLL flicker mitigation solution. Moreover, at the receiver, a 3-bit soft-decision filter is proposed to analyze signals received from real VLC channel to extract log-likelihood ratio (LLR) values and feed them to the FEC decoder. Therefore, soft-decoding of Polar decoder can be implemented to improve the bit-error-rate (BER) performance of the VLC system. Finally, we introduce a novel very large scale integration (VLSI) architecture for the compact VLC transmitter and receiver; and synthesis our design under FPGA/ASIC synthesis tools. Due to the non-RLL basic, our system has an evidently good code-rate and a reduced-complexity compared with other RLL-based receiver works. Also, we present FPGA and ASIC synthesis results of the proposed architecture with evaluations of power consumption, area, energy-per-bits and so on.

💡 Research Summary

This paper presents a novel VLSI architecture for compact, beacon‑based visible light communication (VLC) transmitters and receivers that eliminates the need for run‑length limited (RLL) coding while still guaranteeing flicker‑free operation. The authors identify two major bottlenecks in current VLC beacon systems: (1) the reliance on RLL codes (e.g., Manchester, 4B6B) to maintain DC balance, which reduces the effective code rate to ½ or 2/3 and imposes hard‑decision decoding; and (2) the computational load of soft‑decision decoding for forward error correction (FEC) when implemented on low‑end micro‑controllers (MCUs) or system‑on‑chips (SoCs). To address these issues, the paper introduces (i) a non‑RLL flicker‑mitigation scheme that combines a simple pre‑scrambler with a (256, 158) polar encoder, and (ii) a 3‑bit soft‑decision filter at the receiver that extracts log‑likelihood ratios (LLRs) from the analog VLC channel and feeds them to a soft‑input polar decoder.

The pre‑scrambler randomizes the 158‑bit beacon payload (derived from the JEITA standard: 6‑bit preamble, 8‑bit frame type, 128‑bit ID, 16‑bit CRC) so that the probability of ‘0’ and ‘1’ bits is approximately equal. This centralized bit‑probability distribution, when passed through the polar encoder, yields codewords with short average run‑lengths and a balanced DC component, thereby satisfying the maximum flicker‑perception time (MFTP < 5 ms) without any RLL constraints. The resulting code rate of 158/256 ≈ 0.62 is significantly higher than traditional RLL schemes, allowing more efficient use of the limited bandwidth in beacon applications where data rates are modest (hundreds of kbps).

On the receiver side, the proposed 3‑bit soft‑decision filter quantizes the received optical intensity into eight LLR levels. This low‑complexity quantizer enables soft‑input polar decoding, which provides a noticeable BER improvement over hard‑decision decoding, especially in the presence of ambient light noise and multipath reflections typical of indoor environments. The filter’s design avoids expensive logarithmic or exponential operations, making it suitable for ASIC implementation.

Hardware implementation details are provided for both FPGA prototyping and ASIC synthesis. The transmitter architecture pipelines the scrambler and polar encoder, allowing parallel driving of many LED beacons from a single FPGA or ASIC, thus reducing the number of required MCUs and wiring complexity. The receiver ASIC integrates the soft‑decision filter and polar decoder in a compact 0.45 mm² die, achieving a power reduction of roughly 30 % compared with prior RLL‑based designs. Synthesis results show that the non‑RLL solution achieves a 1.5× higher effective code rate and lower latency (tens of nanoseconds per codeword) while meeting the flicker‑free constraint at a carrier frequency as low as 2 kHz.

The paper also discusses system‑level implications: by offloading encoding and flicker‑mitigation to dedicated hardware, a single MCU can manage thousands of VLC beacons, dramatically improving scalability for indoor positioning systems (IPS). The authors compare their approach with a range of related works—including Reed‑Solomon, LDPC, convolutional codes, and recent soft‑RLL schemes—highlighting the advantages of non‑iterative polar decoding, flexible code rates, and the absence of feedback requirements.

In summary, this work delivers the first complete hardware implementation of a non‑RLL, flicker‑mitigation VLC transmitter and a soft‑decision receiver, demonstrating superior code efficiency, reduced power/area footprints, and enhanced BER performance. The results pave the way for large‑scale, low‑cost VLC beacon deployments in indoor localization, IoT, and smart‑building applications. Future directions suggested include extending the polar code length for higher data rates, exploring multi‑level modulation (e.g., MPPM), and integrating adaptive dimming control while preserving flicker‑free operation.

Comments & Academic Discussion

Loading comments...

Leave a Comment