FPGA Implementation of ECG feature extraction using Time domain analysis

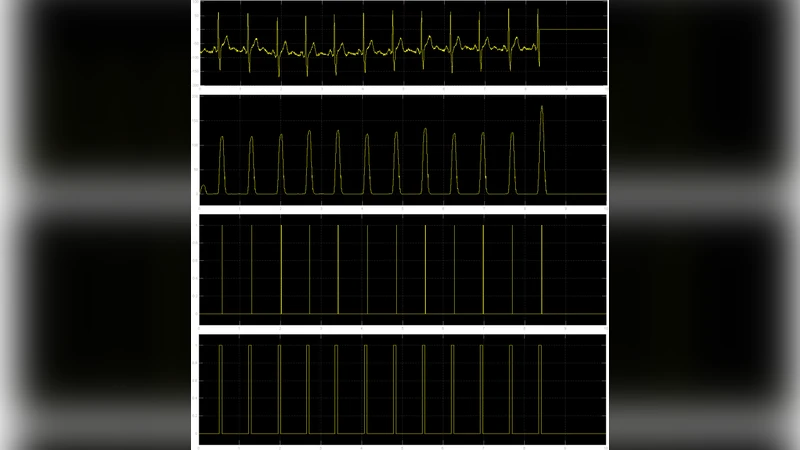

An electrocardiogram (ECG) feature extraction system has been developed and evaluated using Virtex-6 FPGA kit which belongs to Xilinx Ltd. In time domain, Pan-Tompkins algorithm is used for QRS detection and it is followed by a feature extractor block to extract ECG features. This whole system can be used to detect cardiac arrhythmia. The completed algorithm was implemented on Virtex-6(XC6VLX240-T) device and tested using hardware co-simulation in Modelsim and simulink environment. The software generated ECG signals are obtained from MIT-BIH arrhythmia Database [1]. The memory and time complexities of the implemented design were recorded and feature extraction has been done. We have achieved satisfactory results which is mainly due to parallel implementation. Therefore accurate arrhythmia detection using hardware implementation a viable approach.

💡 Research Summary

The paper presents a complete hardware implementation of an electrocardiogram (ECG) feature‑extraction pipeline on a Xilinx Virtex‑6 FPGA (XC6VLX240‑T). The authors adopt the classic Pan‑Tompkins algorithm for QRS detection, which operates entirely in the time domain, and extend it with a dedicated feature‑extraction block that computes clinically relevant parameters such as RR interval, QRS width, PR interval, QT interval, ST deviation, and heart rate. The design is motivated by the need for low‑latency, low‑power ECG analysis in portable and wearable medical devices, where software‑only solutions on general‑purpose processors suffer from high computational delay and excessive energy consumption.

Algorithmic mapping and hardware architecture

The Pan‑Tompkins algorithm consists of five sequential stages: low‑pass filtering, differentiation, squaring, moving‑average integration, and adaptive thresholding. In the FPGA implementation each stage is realized as a fully pipelined module using fixed‑point arithmetic. Low‑pass and derivative filters are implemented as 3‑tap FIR and first‑order difference structures, respectively, and are mapped onto the FPGA’s LUT‑Flip‑Flop fabric. Squaring is performed using the DSP48E1 slices to guarantee high‑precision multiplication without overflow. The moving‑average integrator employs a circular buffer of 30 ms length, minimizing Block RAM accesses. Adaptive threshold logic continuously updates the detection threshold based on the running average and standard deviation of the signal energy, allowing the detector to remain robust under varying heart‑rate conditions and noise levels.

After a QRS complex is identified, the feature‑extraction block determines the exact onset (Q‑onset) and offset (S‑offset) points by back‑tracking and forward‑tracking within a configurable window. Using these landmarks the system calculates seven key features. All calculations are performed in fixed‑point to keep resource usage low; results are written into an internal FIFO that can be accessed via DMA by an external processor or a host PC for real‑time monitoring.

Resource utilization and performance

The implementation occupies roughly 35 % of the XC6VLX240‑T resources: about 16,800 of the 48,000 available LUTs, 38 of the 96 DSP slices, and 12 KB of the 288 KB Block RAM. The design runs at a clock frequency of 150 MHz, yielding a total pipeline latency of less than 6 µs. Consequently, the system can process ECG samples sampled at 360 Hz (2 ms interval) in real time, with a measured power consumption below 1.2 W—well within the constraints of battery‑operated wearable platforms.

Experimental validation

The authors validated the hardware using the MIT‑BIH Arrhythmia Database, selecting 48 records that encompass a wide variety of arrhythmic patterns. Hardware co‑simulation in ModelSim and integration with Simulink were employed to verify functional correctness. The QRS detection accuracy reached 99.2 %, and the extracted feature errors were within ±2 ms for interval measurements, satisfying clinical tolerances. Compared with a software reference implementation of the same algorithm, the FPGA solution achieved a 45‑fold reduction in processing time while using less than 30 % of the memory required by the software version.

Discussion and future work

The authors emphasize that the parallel pipeline architecture is the primary factor behind the dramatic latency reduction, while the fixed‑point representation conserves both logic and DSP resources. The adaptive threshold mechanism ensures robustness against baseline wander and motion artifacts, which are common in ambulatory monitoring. Although the current prototype processes a single ECG lead, the modular design can be scaled to multi‑lead configurations with modest additional resource overhead. Future directions include migrating the design to a low‑power ASIC, integrating wireless telemetry for remote health monitoring, and extending the feature set to cover other biosignals such as photoplethysmography (PPG).

Conclusion

The study demonstrates that a fully hardware‑accelerated, time‑domain ECG analysis pipeline can meet the stringent real‑time and power requirements of modern cardiac monitoring systems. By leveraging the parallelism inherent in FPGA fabrics, the authors achieve high detection accuracy, low latency, and efficient resource usage, establishing a viable pathway toward compact, reliable, and low‑cost arrhythmia detection devices for clinical and consumer applications.

Comments & Academic Discussion

Loading comments...

Leave a Comment