PACER: Peripheral Activity Completion Estimation and Recognition

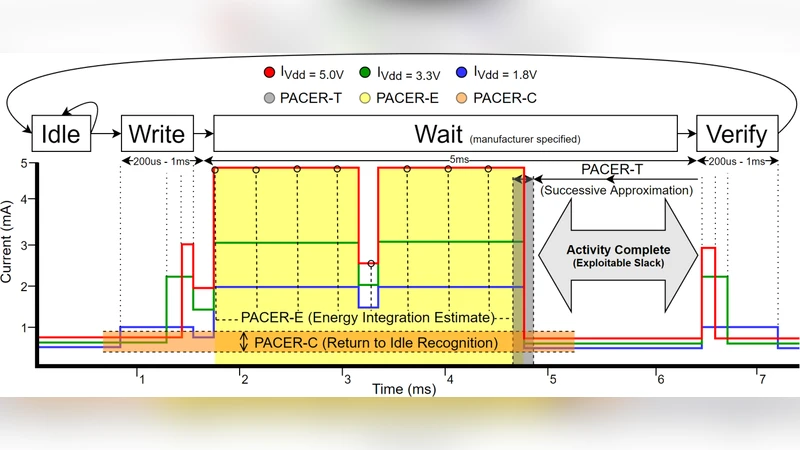

Embedded peripheral devices such as memories, sensors and communications interfaces are used to perform a function external to a host microcontroller. The device manufacturer typically specifies worst-case current consumption and latency estimates for each of these peripheral actions. Peripheral Activity Completion, Estimation and Recognition (PACER) is introduced as a suite of algorithms that can be applied to detect completed peripheral operations in real-time. By detecting activity completion, PACER enables the host to exploit slack between the worst-case estimate and the actual response time. These methods were tested independently and in conjunction with IODVS on multiple common peripheral devices. For the peripheral devices under test, the test fixture confirmed decreases in energy expenditures of up to 80% and latency reductions of up to 67%.

💡 Research Summary

The paper introduces PACER (Peripheral Activity Completion Estimation and Recognition), a suite of three lightweight heuristics designed to detect the exact moment a peripheral operation finishes, thereby allowing the host microcontroller to eliminate unnecessary waiting and polling. Traditional embedded designs rely on manufacturer‑specified worst‑case (WC) latency and current figures, which guarantee correctness but often over‑estimate the true execution time because of temperature, aging, voltage variations, cache effects, and other dynamic factors. This conservatism leads to wasted energy and increased latency, especially when the MCU must stay active to poll status registers or keep communication drivers running.

PACER addresses this inefficiency with three complementary methods:

-

PACER‑T (Timing Heuristic) – Suited for peripherals whose operation time is relatively deterministic (e.g., flash or EEPROM writes). It employs a successive‑approximation algorithm: starting from the WC delay, the MCU halves the wait time after each successful early‑completion detection (Pass) and increases it by half the distance to the last successful value after a failure (Fail). The algorithm converges quickly to the tightest safe delay with minimal computational overhead, enabling the MCU to resume useful work as soon as the peripheral signals completion.

-

PACER‑E (Energy Heuristic) – Targets devices whose current draw varies but whose total energy (charge) required for a given operation is fixed, such as operations that charge an internal capacitor or inductor. The MCU continuously samples voltage and current, digitally integrates them to obtain cumulative charge, and compares the result to a pre‑defined energy threshold. When the threshold is reached, the peripheral is considered done. This method is slightly slower than PACER‑T because of the integration step, but it provides accurate early‑completion detection for variable‑current operations like flash programming.

-

PACER‑C (Current Heuristic) – Designed for highly non‑deterministic activities (e.g., wireless transmissions, Ethernet frames, or memory accesses affected by cache hits). It records the idle current of the device, sets a threshold (empirically 110 % of idle), and waits for a minimum latency period. The operation is declared complete once the measured current falls back below the threshold. This approach is the simplest to implement but is sensitive to supply noise and may generate false positives if the idle current fluctuates.

The authors also discuss integration with Intra‑Operation Dynamic Voltage Scaling (IODVS). IODVS reduces energy by placing the MCU and peripheral in separate voltage domains during the peripheral’s voltage‑independent waiting phase. Because the domains are isolated, the MCU cannot poll the peripheral directly, making PACER essential for reclaiming the slack that IODVS creates.

Experimental Platform – The team built a testbed around an STM32F429 MCU on a custom PRIME board. High‑speed (1 MS/s) four‑channel ADCs, DMA‑driven sampling, and a Maxim MAX4377HAUA+ dual‑current‑sense front‑end provided precise voltage and current measurements. Each peripheral could be powered from an independently switchable voltage rail via a PPS‑330D switch, allowing per‑device isolation without physically disconnecting other components. The setup recorded up to 8 MB per test (50 repetitions per device) and used a 120 Mbps USB link for data offload.

Devices Tested – NAND and NOR flash memories, a commercial EEPROM, a temperature/humidity sensor, and four independent micro‑SD cards. For memories, correctness was verified by read‑back; for the sensor, a status bit indicated operation progress.

Results – Across the board, PACER combined with IODVS achieved up to 80 % reduction in energy consumption and up to 67 % reduction in latency compared with the manufacturer‑specified WC delays. Specific highlights include:

- Flash write (PACER‑T): WC 5 ms wait reduced to ~1.75 ms, a 67 % latency cut.

- EEPROM write (PACER‑E): Energy‑based early detection saved up to 80 % of the energy normally spent during the mandatory wait.

- Sensor read (PACER‑C): Simple current‑threshold detection reliably identified completion, cutting unnecessary MCU active time.

Critical Assessment – The approach relies on a 1 MS/s sampling rate; higher‑frequency current transients could be missed, potentially affecting detection accuracy for very fast peripherals. Threshold values were chosen empirically and may need dynamic adaptation to temperature or aging effects. The paper does not explore machine‑learning‑based classifiers, which could further improve robustness at the cost of higher computational load. Nonetheless, the authors demonstrate that even with modest hardware, substantial power and time savings are achievable.

Conclusion and Outlook – PACER provides a practical, low‑overhead framework for real‑time peripheral completion detection, complementing voltage‑scaling techniques like IODVS. Its three heuristics cover a wide spectrum of peripheral behaviors, making it applicable to battery‑powered IoT nodes, wireless sensor networks, and any low‑power embedded platform where every micro‑joule counts. Future work could focus on adaptive threshold tuning, integration of multi‑modal features (current, voltage, temperature), and validation on ultra‑low‑power MCUs to broaden the impact of this methodology.

Comments & Academic Discussion

Loading comments...

Leave a Comment