A Compact CMOS Memristor Emulator Circuit and its Applications

Conceptual memristors have recently gathered wider interest due to their diverse application in non-von Neumann computing, machine learning, neuromorphic computing, and chaotic circuits. We introduce a compact CMOS circuit that emulates idealized memristor characteristics and can bridge the gap between concepts to chip-scale realization by transcending device challenges. The CMOS memristor circuit embodies a two-terminal variable resistor whose resistance is controlled by the voltage applied across its terminals. The memristor ‘state’ is held in a capacitor that controls the resistor value. This work presents the design and simulation of the memristor emulation circuit, and applies it to a memcomputing application of maze solving using analog parallelism. Furthermore, the memristor emulator circuit can be designed and fabricated using standard commercial CMOS technologies and opens doors to interesting applications in neuromorphic and machine learning circuits.

💡 Research Summary

This paper presents the design, simulation, and application of a compact CMOS-based circuit that emulates the fundamental characteristics of an ideal memristor. Recognizing the practical challenges hindering the widespread adoption of physical memristive devices (ReRAM)—such as device variability, low on-resistance leading to high drive power, and endurance issues—the authors propose a complementary metal-oxide-semiconductor (CMOS) emulator as a low-risk alternative for system-level exploration of memcomputing and neuromorphic architectures.

The core circuit operates on a straightforward yet elegant principle. It employs an n-channel MOSFET (M1) as a floating variable resistor between two terminals (A and B). The resistance of M1 is dynamically controlled by a gate voltage (V_G), which represents the “state” of the memristor. This state voltage is generated by sensing the voltage difference (V_AB) across the terminals using a transconductor (Gm). The Gm converts V_AB into a small current, which is then integrated over time onto a capacitor (Cm). A switch (M_sw) allows this capacitor to hold the integrated charge, implementing a sample-and-hold function that provides short-term analog memory. Positive V_AB increases V_G, decreasing the resistance, and vice versa, perfectly capturing the memristive relationship where the device’s conductance is a function of the history of the applied voltage.

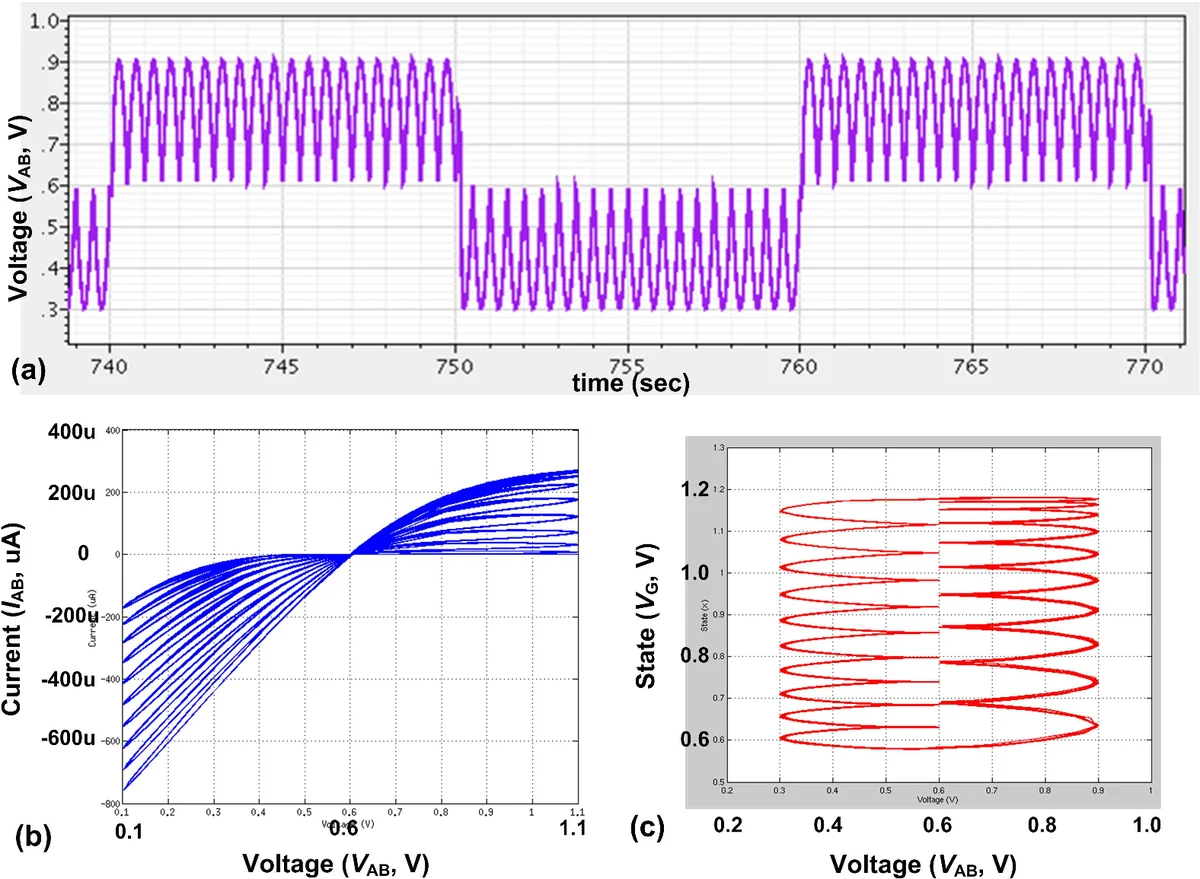

The circuit was designed and simulated in a 130nm CMOS process. Simulation results confirm key memristor fingerprints: a pinched hysteresis loop passing through the origin in the current-voltage characteristic when driven by a sinusoidal signal, and the progressive collapse of this loop into a straight line as the input frequency increases. The circuit also demonstrates monotonic, incremental updates to its state (V_G) in response to pulsed inputs, mimicking the behavior of an analog synapse suitable for machine learning.

To demonstrate its utility in memcomputing—a paradigm that uses memory elements for parallel analog computation—the authors apply the emulator circuit to solve a 2D maze. They construct an 8x8 network where each cell contains two CMOS memristor emulators and switches. By applying DC voltages at the entrance and exit nodes and enabling the network, the memristors along the correct solution path reduce their resistance (increase conductance) faster than those in dead ends, effectively “illuminating” the solution. The result is read out by comparing the state voltages of all memristors after a set time period. This application showcases the potential for using such emulator-based networks to solve complex problems through inherent analog parallelism.

In conclusion, the paper offers a practical and flexible bridge between memristor theory and chip-scale system design. The proposed CMOS memristor emulator circumvents current device-level challenges, is fully compatible with standard fabrication processes, allows designers to tailor resistance ranges, and opens doors for prototyping novel neuromorphic and memcomputing systems while resistive memory technology matures.

Comments & Academic Discussion

Loading comments...

Leave a Comment