Modeling and Verification for Timing Satisfaction of Fault-Tolerant Systems with Finiteness

The increasing use of model-based tools enables further use of formal verification techniques in the context of distributed real-time systems. To avoid state explosion, it is necessary to construct verification models that focus on the aspects under consideration. In this paper, we discuss how we construct a verification model for timing analysis in distributed real-time systems. We (1) give observations concerning restrictions of timed automata to model these systems, (2) formulate mathematical representations on how to perform model-to-model transformation to derive verification models from system models, and (3) propose some theoretical criteria how to reduce the model size. The latter is in particular important, as for the verification of complex systems, an efficient model reflecting the properties of the system under consideration is equally important to the verification algorithm itself. Finally, we present an extension of the model-based development tool FTOS, designed to develop fault-tolerant systems, to demonstrate %the benefits of our approach.

💡 Research Summary

The paper addresses the challenge of verifying timing satisfaction in distributed real‑time fault‑tolerant systems while avoiding the state‑explosion problem that typically hampers formal verification. It proposes a systematic methodology that starts from a high‑level system model, transforms it into a compact verification model, and applies theoretical reduction techniques to keep the model size manageable for model‑checking tools such as UPPAAL.

First, the authors examine the limitations of classical timed automata (TA) for representing distributed real‑time behavior. Standard TA assume a finite set of clocks with linear constraints and treat communication channels as instantaneous synchronizations. In practice, distributed systems exhibit variable network delays, dynamic scheduling policies, and non‑linear clock updates, which cause TA to either lose fidelity or generate an intractably large state space. To mitigate this, the paper introduces the notion of “Restricted Timed Automata” (RTA). An RTA limits clock resets and guard conditions to a predefined finite set, abstracts communication links as bounded FIFO buffers, and restricts clock expressions to linear inequalities. This restriction guarantees a finite reachable state space while preserving the essential timing properties needed for deadline analysis.

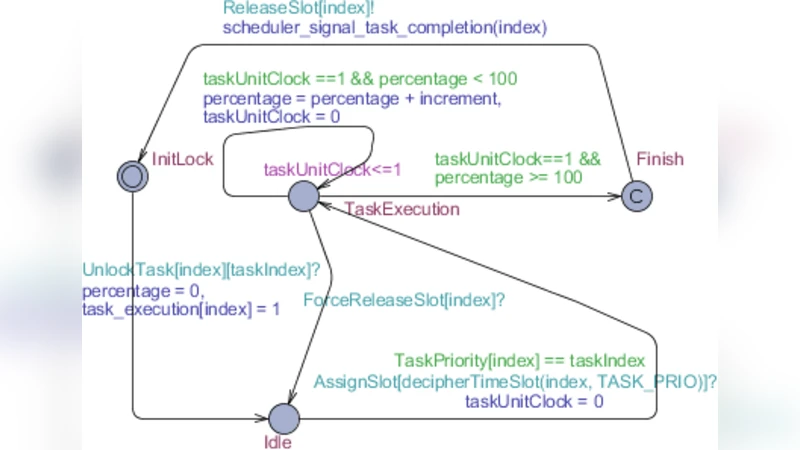

Second, the paper formalizes a model‑to‑model transformation function 𝑇: SM → VM, where SM denotes the original system model and VM the verification model. The transformation proceeds in three steps: (1) each component’s execution flow is mapped to a set of locations and edges in the RTA; (2) inter‑component messages are replaced by synchronized channels that respect the FIFO abstraction; (3) fault injection points are encoded as special “fault transitions” equipped with guard predicates and clock resets that model the occurrence and recovery of faults. The authors prove a preservation theorem: if the SM satisfies a given timing property (e.g., “no deadline miss”), then the transformed VM satisfies the same property under the semantics of RTA. This theorem ensures that verification results on the reduced model are sound with respect to the original system.

Third, the paper presents two theoretical criteria for reducing the size of the verification model without sacrificing correctness. The first criterion, “Redundant Timing Information Elimination,” merges states that share identical clock constraints, effectively collapsing equivalent timing regions. The second criterion, “Equivalence‑Class Merging,” identifies sets of execution paths that are behaviorally indistinguishable with respect to the property of interest and replaces them with a single abstract path. Both criteria rely on language equivalence and timed‑language inclusion checks, which are performed using regular‑language techniques and simulation relations. By applying these reductions, the reachable state space can be decreased exponentially, making model checking feasible for systems that would otherwise be out of reach.

To demonstrate the practicality of the approach, the authors extend the model‑based development tool FTOS (Fault‑Tolerant Operating System). FTOS originally supports functional fault‑tolerance analysis; the extension adds a timing‑verification workflow that automatically generates the RTA, applies the reduction criteria, and invokes UPPAAL for deadline verification. The case study focuses on an avionics control system with multiple redundant sensors, communication buses, and a fault‑recovery protocol. The transformed verification model contains roughly 30 % of the states of the naïve TA representation, and verification time drops from several minutes to under a minute on a standard workstation. Moreover, the analysis successfully identifies a scenario where a combined sensor fault and network delay would cause a deadline miss, allowing designers to adjust the recovery schedule early in the development cycle.

In conclusion, the paper contributes a complete pipeline—from high‑level system description to a compact, formally verified timing model—tailored for fault‑tolerant distributed real‑time systems. The introduction of Restricted Timed Automata, the mathematically proven transformation, and the reduction criteria together address both the expressiveness and scalability issues that have limited the adoption of formal timing verification in industry. Future work is suggested in three directions: extending RTA to handle non‑linear clock updates, incorporating probabilistic delay models, and automating the selection of optimal reduction strategies based on property‑specific heuristics. Overall, the research offers a viable path for integrating rigorous timing analysis into model‑based design workflows for safety‑critical cyber‑physical systems.

Comments & Academic Discussion

Loading comments...

Leave a Comment